digital

# RIOI/RIO2 DISK SUBSYSTEM USER'S GUIDE

# RL01/RL02 Disk Subsystem User's Guide

1st Edition, December 1978 2nd Printing (Rev), September 1979

### Copyright © 1978, 1979 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape DECUS

DIGITAL Digital Logo Omnibus

PDP Q-Bus Unibus

VAX

### TABLE OF CONTENTS

| CHAPTER 1        | INTRODUCTION                  |      |

|------------------|-------------------------------|------|

| 1.1              | PURPOSE AND SCOPE             | 1-1  |

| 1.2              | REFERENCE DOCUMENTS           | 1-1  |

| 1.3              | SUBSYSTEM CONFIGURATIONS      | 1-1  |

| 1.3.1            | RL01/RL02 Disk Drive          | 1-2  |

| 1.3.2            | RL Controllers                | 1-2  |

| 1.3.2.1          | RL11 Controller Description   | 1-2  |

| 1.3.2.2          | RLV11 Controller Description  | 1-3  |

| 1.3.2.3          | RL8A Controller Description   | 1-3  |

| 1.3.3            | RL01K/RL02K Disk Cartridge    | 1-3  |

| 1.3.3.1          | Interchangeability            | 1-4  |

| 1.3.3.2          | Sector Format                 | 1-4  |

| 1.4              | SECTOR LOCATION               | 1-6  |

| 1.5              | BAD SECTOR FILE               | l-6  |

| 1.6              | RL01/RL02 SPECIFICATIONS      | 1-9  |

| CHAPTER 2        | INSTALLATION                  |      |

| 2.1              | SITE PREPARATION AND PLANNING | 2-1  |

| 2.1.1            | Environmental Considerations  | 2-1  |

| 2.1.1.1          | Cleanliness                   | 2-1  |

| 2.1.1.2          | Space Requirements            | 2-1  |

| 2.1.1.3          | Floor Loading                 | 2-1  |

| 2.1.1.4          | Heat Dissipation              | 2-1  |

| 2.1.1.5          | Acoustics                     | 2-2  |

| 2.1.1.6          | Temperature                   | 2-2  |

| 2.1.1.7          | Relative Humidity             | 2-2  |

| 2.1.1.8          | Altitude                      | 2-2  |

| 2.1.1.9          | Power and Safety Precautions  | 2-2  |

| $2.1.\bar{1}.10$ | Radiated Emissions            | 2-2  |

| 2.1.1.11         | Attitude/Mechanical Shock     | 2-3  |

| 2.1.2            | Options                       | 2-3  |

| 2.1.3            | AC Power Requirements         | 2-5  |

| 2.1.3.1          | Standard Applications         | 2-5  |

| 2.1.3.2          | Optional Applications         | 2-5  |

| 2.1.4            | Installation Constraints      | 2-7  |

| 2.1.5            | Grounding Requirements        | 2-7  |

| 2.2              | AC CABLING                    | 2-8  |

| 2.3              | INSTALLATION - GENERAL        | 2-10 |

| 2.4              | RL11 CONTROLLER INSTALLATION  | 2-10 |

| 2.5              | RLV11 CONTROLLER INSTALLATION | 2-16 |

| 2.5.1            | Bus Interface Module          | 2-16 |

| 2.5.2            | Drive Module                  | 2-18 |

| 2.5.3            | Module Slot Location          | 2-18 |

| 2.5.5            | Module Installation           | 2-18 |

# TABLE OF CONTENTS (CONT)

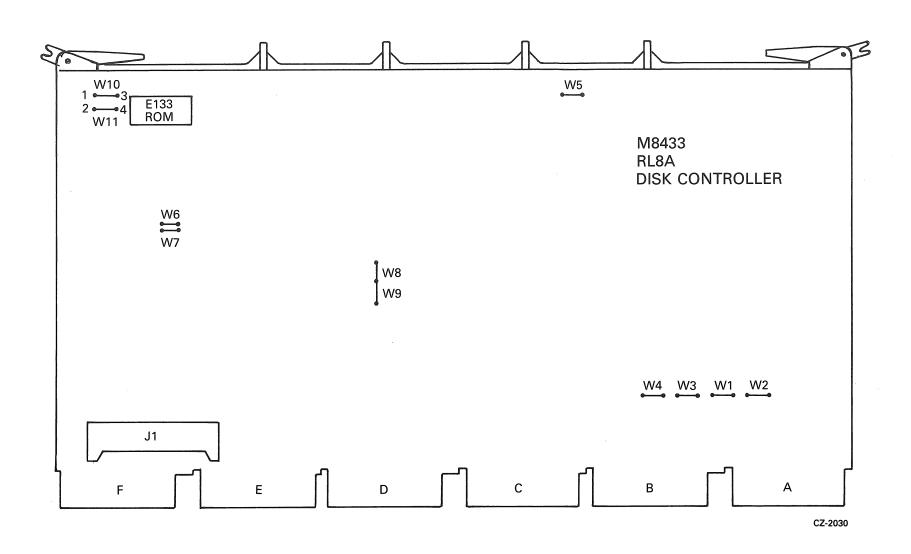

| 2.6            | RL8-A CONTROLLER INSTALLATION                  | 2-20 |

|----------------|------------------------------------------------|------|

| 2.6.1          | Introduction                                   | 2-20 |

| 2.6.2          | Module Slot Location                           | 2-20 |

| 2.6.3          | Module Installation                            | 2-20 |

| 2.7            | RL01/RL02 DISK DRIVE INSTALLATION              | 2-22 |

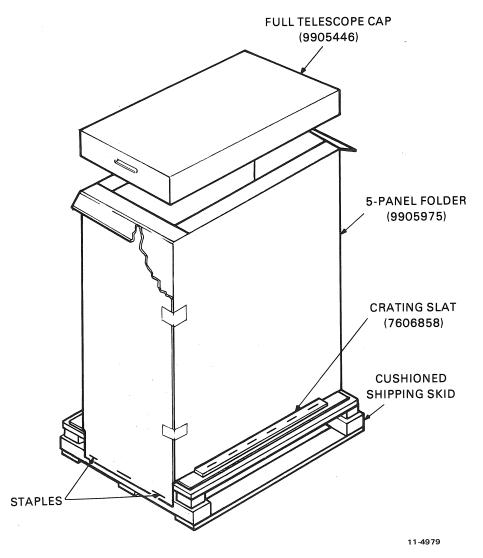

| 2.7.1          | Unpacking and Inspection                       | 2-22 |

| 2.7.2          | RL01/RL02 Disk Drive Unit Mounting             | 2-23 |

| 2.7.3          | Drive Prestart Inspection                      | 2-27 |

| 2.7.4          | Drive Startup Operation Check                  | 2-30 |

| 2.8            | CONFIDENCE TESTING                             | 2-30 |

| 2.8.1          | RL11-Based Diagnostics                         | 2-31 |

| 2.8.2          | RLV11-Based Diagnostics                        | 2-33 |

| 2.8.3          | RL8A-Based Diagnostics                         | 2-33 |

| 2.9            | USE OF THE M9312 BOOTSTRAP WITH AN RL11 SYSTEM | 2-35 |

| CHAPTER 3      | OPERATOR'S GUIDE                               |      |

| 2.1            | NAME OF A CONTROL OF                           |      |

| 3.1            | INTRODUCTION                                   | 3-1  |

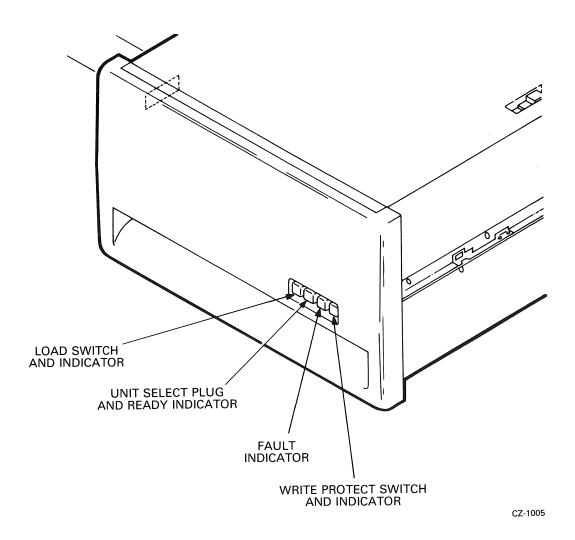

| 3.2            | CONTROLS AND INDICATORS                        | 3-1  |

| 3.2.1          | Power On/Off Circuit Breaker                   | 3-2  |

| 3.2.2          | RUN/STOP Switch with Load Indicator            | 3-2  |

| 3.2.3          | UNIT SELECT Switch with READY Indicator        | 3-3  |

| 3.2.4<br>3.2.5 | FAULT Indicator                                | 3-3  |

| 3.2.3          | WRITE PROTECT Switch and Indicator             | 3-3  |

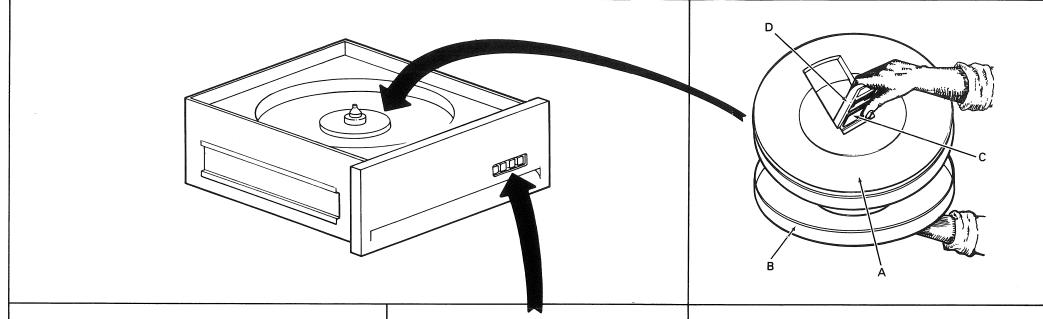

| 3.3.1          | OPERATING PROCEDURES                           | 3-3  |

| 3.3.2          | Cartridge Loading and Drive Startup Procedure  | 3-3  |

| 3.4            | Cartridge Unloading Procedure                  | 3-4  |

| 3.4.1          | OPERATOR MAINTENANCE                           | 3-7  |

| 3.4.2          | Introduction                                   | 3-7  |

| 3.4.3          | Professional Cartridge Cleaning                | 3-7  |

| 3.4.4          | User Cartridge Cleaning                        | 3-7  |

| 3.5            | Spindle Assembly Cleaning                      | 3-7  |

| 3.3            | CARTRIDGE CARE SUMMARY                         | 3-/  |

| CHAPTER 4      | RL11/RLV11 PROGRAMMING INFORMATION             |      |

| 4.1            | GENERAL DESCRIPTION                            | 4-1  |

| 4.1.1          | RL11 Controller Description                    | 4-1  |

| 4.1.2          | RLV11 Controller Description                   |      |

| 4.2            | ADDRESSABLE REGISTERS                          | 4-1  |

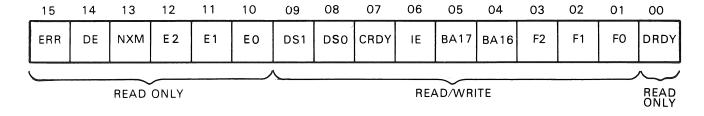

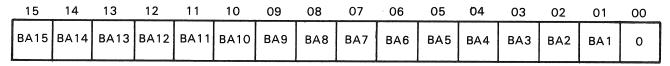

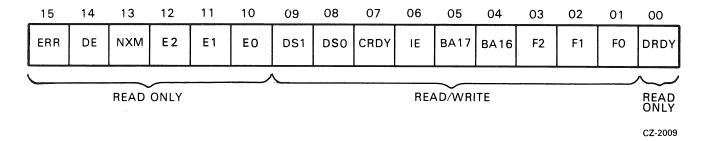

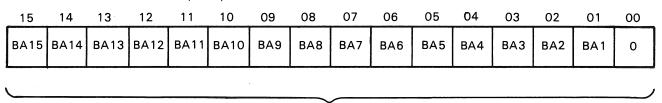

| 4.2.1          | Control Status Register                        | 4-1  |

| 4.2.2          | Bus Address Register                           | 4-4  |

| 4.2.3          | Disk Address Register                          | 4-5  |

| 4.2.3.1        | DA Register During a Seek Command              | 4-5  |

| 4.2.3.2        | DA Register During Read or Write Data Command  | 4-5  |

| 4.2.3.3        | DA Register During a Get Status Command        |      |

| 4.2.4          | Multipurpose Register                          |      |

### TABLE OF CONTENTS (CONT)

| 4.2.4.1   | MP Register After a Get Status Command                 | 4-7  |

|-----------|--------------------------------------------------------|------|

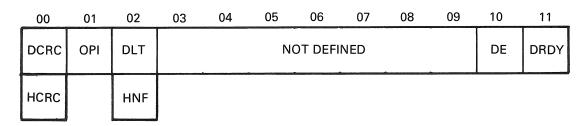

| 4.2.4.2   | MP Register After a Read Header Command                | 4-8  |

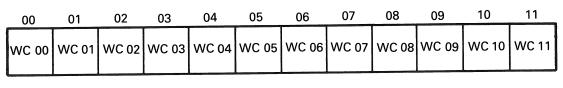

| 4.2.4.3   | MP Register During Read/Write Data Command             | 4-9  |

| 4.2.5     | Register Summary                                       | 4-9  |

| 4.3       | CONTROLLER COMMANDS                                    |      |

| 4.3.1     | No-Op (RL11) or Maintenance (RLV11) - Function Code 0  | 4-12 |

| 4.3.2     | Write Check - Function Code 1                          | 4-13 |

| 4.3.3     | Get Status - Function Code 2                           | 4-13 |

| 4.3.4     | Seek - Function Code 3                                 | 4-13 |

| 4.3.5     | Read Heading - Function Code 4                         | 4-14 |

| 4.3.6     | Write Data - Function Code 5                           | 4-14 |

| 4.3.7     | Read Data - Function Code 6                            | 4-14 |

| 4.3.8     | Read Data Without Header Check - Function Code 7       | 4-14 |

| 4.4       | OPERATIONAL CONSIDERATIONS                             | 4-14 |

| 4.4.1     | Interrupt                                              | 4-14 |

| 4.4.2     | Seek Operation                                         | 4-15 |

| 4.4.3     | Overlapped Seeks                                       | 4-15 |

| 4.4.4     | Data Transfer                                          | 4-15 |

| 4.4.5     | Recovery of Data With Bad Headers                      | 4-15 |

| 4.4.6     | Non-interchangeability of RL01/RL02 Disk Cartridges    | 4-15 |

| 4.4.0     | ERROR RECOVERY                                         | 4-16 |

| 4.6       | DIFFERENCE SUMMARY (RK05 AND RL01/RL02)                | 4-17 |

| 4.6.1     | Spiral Read/Write or Mid-Transfer Seeks                | 4-17 |

| 4.6.2     | Implicit Seeks Versus Explicit Seeks                   | 4-17 |

| 4.6.3     | Recalibrate                                            | 4-17 |

|           | Bad Sector File                                        | 4-18 |

| 4.6.4     | Reformatting                                           | 4-18 |

| 4.6.5     | Seek Interrupt                                         | 4-18 |

| 4.6.6     | Seek Interrupt                                         | 10   |

| CHAPTER 5 | RL8-A PROGRAMMING INFORMATION                          |      |

| 5.1       | GENERAL DESCRIPTION                                    | 5-1  |

| 5.2       | ADDRESSABLE REGISTERS                                  | 5-2  |

| 5.2.1     | Command Register A                                     | 5-2  |

| 5.2.1.1   | Command Register A During a Seek Command               | 5-2  |

| 5.2.1.2   | Command Register A During a Read or Write Data Command | 5-3  |

| 5.2.2     | Command Register B                                     | 5-4  |

| 5.2.3     | Break Memory Address Register                          | 5-5  |

| 5.2.4     | Word Count Register                                    | 5-5  |

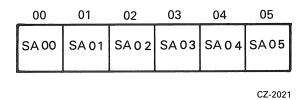

| 5.2.5     | Sector Address Register                                | 5-5  |

| 5.2.6     | Error Register                                         | 5-6  |

| 5.2.7     | Silo Data Buffer                                       | 5-7  |

| 5.2.7.1   | Silo Register After a Get Status Command               | 5-7  |

| 5.2.7.2   | Silo Data Buffer During a Read Header Command          | 5-9  |

| 5.2.8     | Register Summary                                       | 5-9  |

| 5.3       | CONTROLLER COMMANDS                                    | 5-14 |

| 5 3 1     | Maintenance Command                                    | 5-14 |

# **TABLE OF CONTENTS (CONT)**

| 5.3.2      | Reset Command                                          | 5-14 |

|------------|--------------------------------------------------------|------|

| 5.3.3      | Get Status Command                                     |      |

| 5.3.4      | Seek Command                                           | 5-15 |

| 5.3.5      | Read Header Command                                    | 5-15 |

| 5.3.6      | Write Data Command                                     | 5-15 |

| 5.3.7      | Read Data Command                                      |      |

| 5.3.8      | Read Data Without Header Check Command                 |      |

| 5.3.9      | Maintenance Bit                                        | 5-16 |

| 5.4        | OPERATIONAL CONSIDERATIONS                             | 5-18 |

| 5.4.1      | 8-Bit Mode Versus 12-Bit Mode                          |      |

| 5.4.2      | Interrupt                                              |      |

| 5.4.3      | Seek Operation                                         |      |

| 5.4.4      | Overlapped Seeks                                       |      |

| 5.4.5      | Recovery of Data with Bad Headers                      | 5-18 |

| 5.4.6      | Non-interchangeability of Disk Cartridges              | 5-19 |

| 5.4.6.1    | RL01K/RL02K                                            | 5-19 |

| 5.4.6.2    | RL8-A/RL11/RLV11                                       | 5-19 |

| 5.4.7      | Use of Two RL8-A Controllers                           | 5-19 |

| 5.5        | ERROR RECOVERY                                         | 5-19 |

| 5.6        | DIFFERENCE SUMMARY (RK05 and RL01/RL02)                |      |

| 5.6.1      | Spiral Read/Write or Mid-Transfer Seeks                | 5-20 |

| 5.6.2      | Implicit Seeks Versus Explicit Seeks                   |      |

| 5.6.3      | Recalibrate                                            |      |

| 5.6.4      | Bad Sector File                                        |      |

| 5.6.5      | Reformatting                                           |      |

| 5.6.6      | Seek Interrupt                                         | 5-20 |

| APPENDIX A | RL11 CONFIGURATION AND INSTALLATION CONSIDERATIONS     |      |

|            |                                                        |      |

| A-1        | SPC CONSIDERATIONS                                     |      |

| A-2        | CONFIGURATION CONSIDERATIONS                           | A-1  |

|            | FIGURES                                                |      |

| Figure No. | Title                                                  | Page |

| 1-1        | Typical RL01/RL02 Mass Storage Subsystem Configuration | 1-2  |

| 1-2        | RL01/RL02 Disk Drive                                   |      |

| 1-3        | RL01K/RL02K Disk Cartridge Format                      |      |

| 1-4        | Access Method for Sequential Transfers                 |      |

| 1-5        | Sector Relocation                                      |      |

| 1-6        | Bad Sector File Format                                 |      |

| 2-1        | RL01/RL02 Disk Drive-Rear View                         |      |

| 2-2        | Approved Electrical Plugs and Receptacles              |      |

| 2-3        | Power Panel Grounded to Building Frame                 |      |

| 2-4        | Power Panel Grounded to Metal Plate                    | 2-8  |

# FIGURES (CONT)

| 2.5                    | Typical 60 Hz Power System                          | 2-9             |

|------------------------|-----------------------------------------------------|-----------------|

| 2-5                    | Typical 50 Hz Power System                          | 2-10            |

| 2-6<br>2-7             | Split Phase (2-Phase) Power System                  | 2-10            |

| 2-7                    | Three Phase Y Power System                          |                 |

| 2-8<br>2-9             | RL11 Component Layout                               | 2-11            |

| 2-9                    | RL11 Base and Vector Address Jumper Configuration   | 2-13            |

| 2-10                   | RL11 Priority Jumper Assembly Connections           | 2-14            |

| 2-11                   | PI 11 Controller Installation                       |                 |

| 2-12                   | RLV11 Bus Interface Module (M8014) (Component Side) | 2-17            |

| 2-13                   | RLV11 Base Address Switch Settings                  | 2-17            |

| 2-14                   | RLV11 Vector Address Switch Settings                | 2-18            |

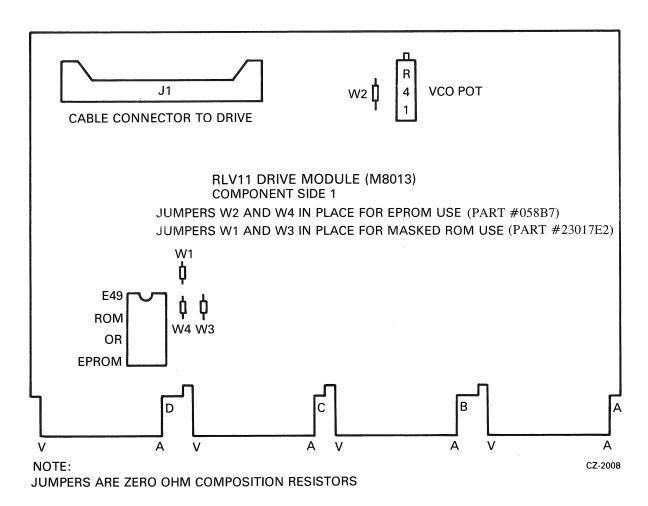

| 2-15                   | RLV11 Drive Module (M8013)                          | 2-19            |

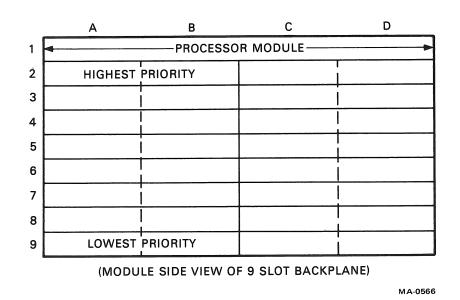

| 2-10                   | H9273 Backplane Grant Priority Structure            | 2-19            |

| 2-17                   | RL8-A Jumpers                                       | 2-21            |

| 2-18                   | HQ50 Shipping Package                               |                 |

| 2-19                   | RL01/RL02 Cabinet Installation                      | 2-25            |

| 2-20                   | RL01/RL02 - Covers Removed                          | 2-26            |

| 2-21                   | RL01/RL02 Disk Drive - Rear View                    | 2-27            |

| 2-22                   | PLO1/RLO2 Disk Drive - Front View                   |                 |

| 2-23                   | PI 01/PI 02 Disk Drive - Exposed Drive Logic Module |                 |

| 3-1                    | PI 01/PI 02 Disk Drive - Front View                 |                 |

| 3-1                    | PI 01/PI 02 Disk Drive - Rear View                  |                 |

| 3-3                    | Cartridge Loading Procedure                         |                 |

| 3-3<br>4-1             | CS Pagister                                         |                 |

| 4-1                    | RA Pegister                                         | <del> </del>    |

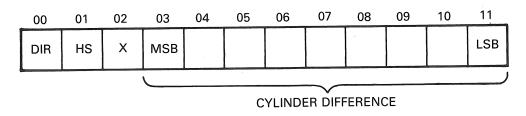

| 4-2<br>4-3             | DAR - Seek Command                                  | 4-5             |

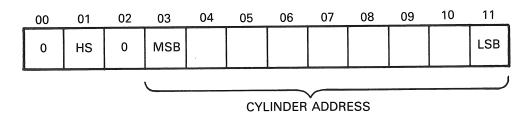

| 4-3<br>4-4             | DAR - Read/Write Data Command                       | 4-6             |

| 4- <del>4</del><br>4-5 | DAR - Get Status Command                            | 4-0             |

| 4-5<br>4-6             | MPR - Status Word                                   | 4-7             |

| 4-0<br>4-7             | MDR - Three Header Words                            | <del>4</del> -0 |

| 4-7<br>4-8             | MPR - Used as a Word Counter                        | 4-9             |

| 4-0<br>4-9             | Register Summary                                    | 4-10            |

| · -                    | Command Register A During a Seek Command            | 5-3             |

| 5-1                    | Command Register A During A Read/Write Data Command | 5-3             |

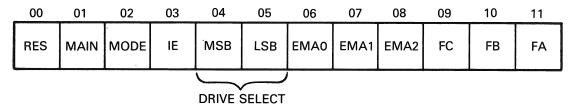

| 5-2                    | Command Register B                                  | 5-4             |

| 5-3                    | Break Memory Address Register                       |                 |

| 5-4                    | Word Count Register                                 |                 |

| 5-5                    | Sector Address Register                             | 5-6             |

| 5-6                    | Error Register                                      | 5-6             |

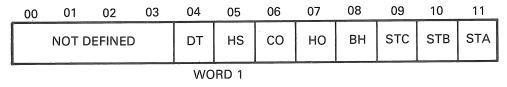

| 5-7                    | Silo Buffer for Status Word 1                       |                 |

| 5-8                    | Silo Buffer for Status Word 2                       |                 |

| 5-9                    | Silo Buffer for Header Words                        | 5-10            |

| 5-10                   | Register Summary                                    | 5-11            |

| 5-11                   | Maintenance Mode Bit                                | 5-17            |

| 5-12                   | Maintenance Mode Dit                                |                 |

### **TABLES**

| Table No. | Title                                                          | Page |

|-----------|----------------------------------------------------------------|------|

| 1-1       | Reference Documents                                            |      |

| 1-2       | RL01/RL02 Disk Drive Physical and Environmental Specifications | 1-9  |

| 1-3       | RL01/RL02 Disk Drive Operational Specifications                | 1-11 |

| 1-4       | RL01K/RL02K Disk Cartridge Specifications                      | 1-12 |

| 2-1       | Saleable RL01/RL02 Subsystem Options                           | 2-3  |

| 2-2       | Saleable Cabinet Options                                       | 2-4  |

| 2-3       | Diagnostic Catalogs and Indexes                                | 2-31 |

| 2-4       | RL11-Based Diagnostics                                         | 2-31 |

| 2-5       | RL11 Diagnostic Kit Numbers                                    |      |

| 2-6       | RL11 Diagnostic Components                                     |      |

| 2-7       | User Documents                                                 | 2-33 |

| 2-8       | RLV11 Diagnostic Kit Designations                              | 2-33 |

| 2-9       | RL8/RL01 Diagnostic Kits                                       | 2-33 |

| 2-10      | RL8/RL01 Diagnostic Components                                 | 2-34 |

| 2-11      | RL8/RL02 Diagnostic Kits                                       | 2-34 |

| 2-12      | RL8/RL02 Diagnostic Components                                 | 2-35 |

| 4-1       | Controller Addressable Registers                               | 4-2  |

| 4-2       | RL11/RLV11 Controller Commands                                 | 4-12 |

| 4-3       | Errors                                                         | 4-16 |

| 5-1       | RL8-A Instruction Set                                          |      |

| 5-2       | RL8-A Controller Commands                                      |      |

| 5-3       | Errors                                                         | 5-19 |

# CHAPTER 1 INTRODUCTION

#### 1.1 PURPOSE AND SCOPE

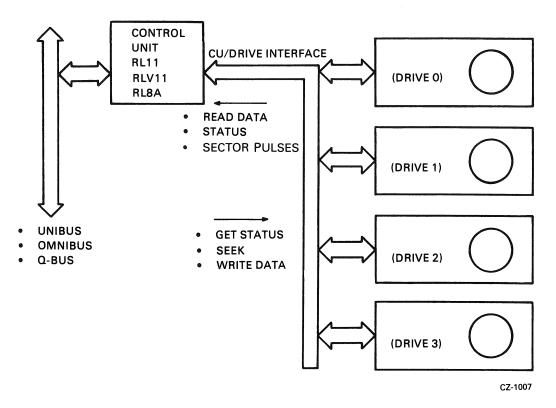

This manual provides information on the capabilities, installation, operation, and programming of the RL01/RL02 Disk Subsystem. The basic subsystem comprises one RL11, RLV11 or RL8A controller and up to four RL01 or RL02 Disk Drives.

This manual is intended primarily for operating and programming personnel. Service should be performed only by qualified Digital field engineering and maintenance personnel. A prerequisite for understanding this manual is a basic knowledge of PDP-8 and PDP-11 processors and peripherals.

#### 1.2 REFERENCE DOCUMENTS

Table 1-1 lists the documents that will be available to provide the information necessary for a complete understanding of the function, theory and maintenance of the RL01/RL02 Disk Drives and the RLV11/RL8-A Controllers. The Unibus and LSI-11 Bus are described in the *PDP11 Bus Handbook* (EB-17525). The Omnibus is described in the *PDP8/A Miniprocessor User's Manual* (EK-8A002-MM).

**Table 1-1 Reference Documents**

| Title                                                                                                                                                                                                                                                                                                                                                                | Document No.                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| RL01/RL02 Disk Drive Technical Manual RL01 Disk Drive Illustrated Parts Breakdown RL02 Disk Drive Illustrated Parts Breakdown RL01/RL02 Disk Subsystem Preventive Maintenance Manual * RL01/RL02 Disk Drive Pocket Service Guide RL11 Controller Technical Description Manual RLV11 Controller Technical Description Manual RL8A OMNIBUS Controller Technical Manual | EK-RL012-TM<br>EP-00016-IP<br>EP-00016-IP<br>EP-00008-PM<br>EK-RL012-PG<br>EK-0RL11-TD<br>EK-RLV11-TD<br>EK-RLV11-TD |

<sup>\*</sup> NOTE - This document is only available to Digital Equipment Corporation Service personnel.

#### 1.3 SUBSYSTEM DESCRIPTION

The RL01/RL02 mass storage subsystem is based on the RL01K/RL02K disk cartridges, the RL01/RL02 drive unit(s), and an appropriate controller such as the RL11 (PDP-11), RLV11 (LSI-11), or RL8A (PDP-8). The basic subsystem is illustrated in Figure 1-1.

Figure 1-1 Typical RL01/RL02 Mass Storage Subsystem

Configuration

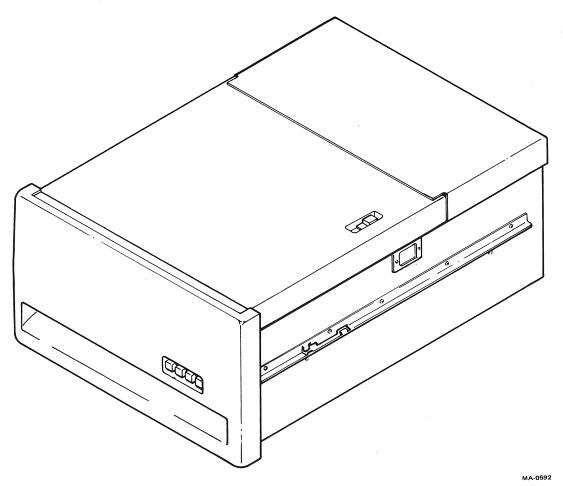

#### 1.3.1 RL01/RL02 Disk Drive

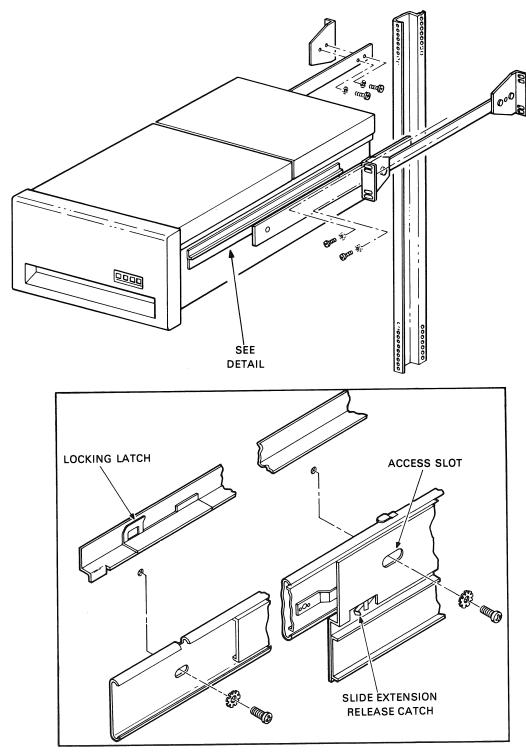

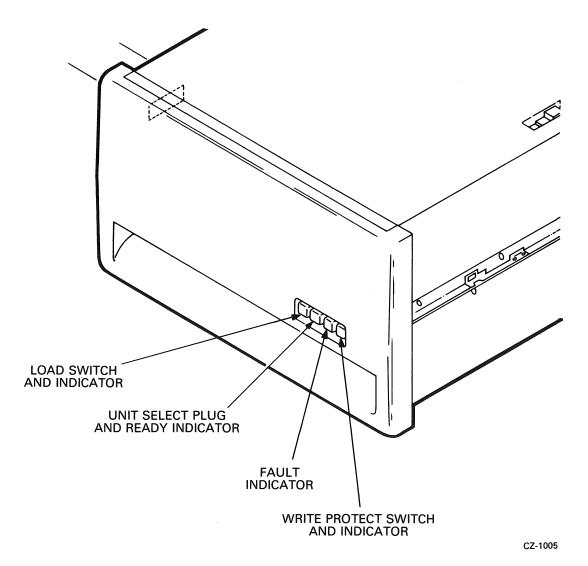

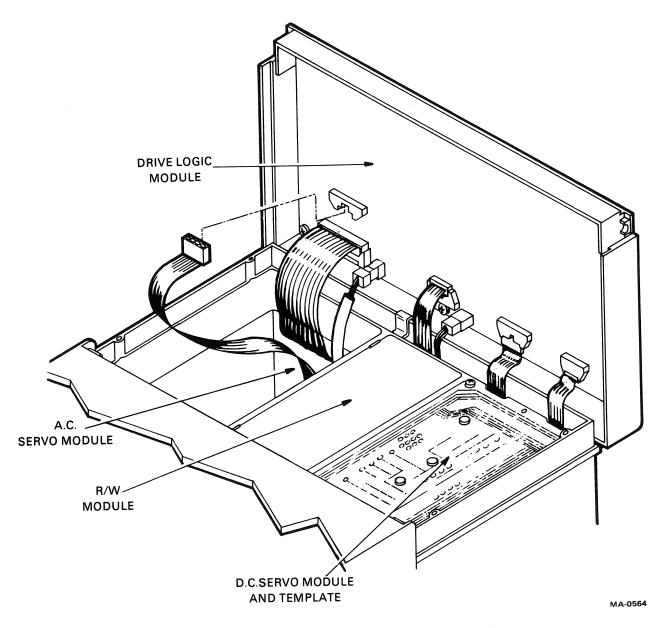

The RL01/RL02 drive unit is built into a chassis that slides out of the cabinet to allow the operator access to the top cover for loading and unloading of the disk cartridge. If the stops on the slide are manually released the chassis can be pulled farther out so that the rear top cover can be removed for servicing. The front panel contains operator controls and indicators.

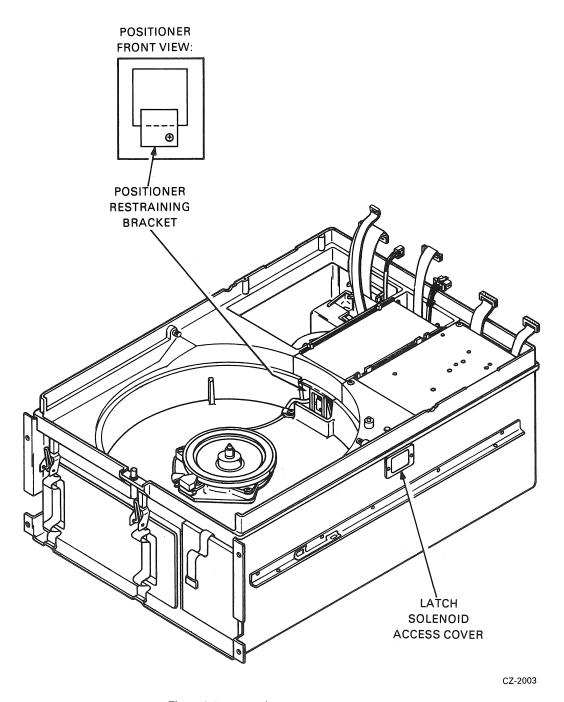

The chassis contains a spindle, two read/write heads mounted on a positioner, logic modules, a power supply with an ac power cord and circuit breaker, a closed-loop clean air system, a cooling air system, appropriate safety interlocks, and connectors for the I/O cable(s).

The drive unit is shown in Figure 1-2.

The RL02 drive unit has a label reading "RL02" on the front panel. The RL01 drive currently does not have a label identifying it as an RL01.

#### 1.3.2 RL Controllers

There are three controllers available for the RL01/RL02 subsystem. All can handle up to four drives and all feature Direct Memory Access (DMA) operation.

**1.3.2.1 RL11 Controller Description** — The RL11 Controller consists of a single, hex-height Small Peripheral Controller (SPC) module designated M7762. It is used to interface the drive with the PDP-11 Unibus. The data is formatted in 16-bit words. This controller can handle any combination of up to four RL01 and/or RL02 Drives.

**1.3.2.2 RLV11 Controller Description** — The RLV11 Controller consists of two quad-height modules designated M8013 and M8014. This controller interfaces the drive with the LSI-11 Bus. The data is formatted in 16-bit words. This controller can handle any combination of up to four RL01 and/or RL02 Drives.

**1.3.2.3 RL8A Controller Description** — The RL8A Controller consists of a single, hex-height module designated M8433. It is used to interface the drive with the PDP-8 Omnibus. The data can be formatted in either 8-bit bytes or 12-bit words. This controller has a jumper-determined choice of handling RL01 or RL02 Drives. However, in the RL02-jumpered configuration, it can handle any combination of up to four RL01 and/or RL02 Drives.

1.3.3 RL01K/RL02K Disk Cartridge

The RL01K or RL02K is a removable, top-loading 5440-type disk cartridge that is formatted in a manner unique to the RL01/RL02 subsystem. Both cartridges contain a single platter. The RL01K cartridge has a capacity of 5.2 megabytes of user data, and the RL02K cartridge will hold 10.4 megabytes of data. Both sides of the platter are used for data. There are 256 tracks on each RL01K platter surface and 512 tracks on each RL02K platter surface. Each track is divided into 40 sectors. Each sector contains 256 bytes of data. The last track of the last surface is reserved for the cartridge serial number and bad sector information. Head positioning servo information and header information are prerecorded at the factory and cannot be reformatted in the field. This information, along with the data, is read by the read/write heads but the internal logic of the drive unit protects the servo and header information from being overwritten.

Figure 1-2 RL01/RL02 Disk Drive

**1.3.3.1 Interchangeability** – The RL01K and RL02K Disk Cartridges are not functionally interchangeable although they are physically interchangeable. It is possible to mount an RL01K cartridge on an RL02 drive, for example, but proper operation will not occur. An RL01K cartridge written on an RL01 unit can be read on any other RL01 unit even if that unit is controlled by a different type of controller. The only limitation to this interchangeability is that if an RL8A controller is used to write data and the cartridge is to be used on a drive controlled by an RL11 or an RLV11 controller, the RL8A must use an 8-bit byte mode of operation.

An RL02K cartridge written on an RL02 unit can be read on any other RL02 unit (assuming the same conditions mentioned above).

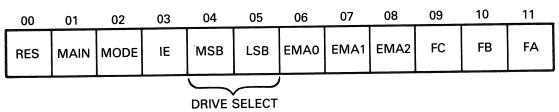

#### **1.3.3.2** Sector Format – As shown in Figure 1-3, each sector contains:

- Servo information for head positioning

- Header (address) information

- Data 128 words of 16 bits each, or 256 bytes of 8 bits each, or 170 words of 12 bits each

Only the data portion of a sector can be written by the user. The servo and header information is protected by the drive logic and controller to ensure disk integrity and cannot be written in the field.

Each sector starts with a sector pulse that is produced by a sector transducer mounted on the drive unit. It senses the sector notches that are machined into the hub of the disk cartridge.

During the time that sector notch passes by the sector transducer, the heads detect two servo pulse bursts (S1 and S2) that are prerecorded on the platter. These servo bursts are used by the drive logic for head positioning.

Following the servo pulse bursts is the header. It consists of:

- A preamble of three words 47 "0" bits and one "1" bit

- A word that contains the address sector, head, and cylinder

- A word of all zeroes

- A word containing information created by the Cyclic Redundancy Check (CRC) logic

- A one-word postamble of all zeroes

Following the header is the user writable data area. It consists of:

- A preamble of three words 47 "0" bits and one "1" bit

- Data (128 words of 16 bits or 256 bytes of 8 bits or 170 words of 12 bits)

- A word containing CRC-generated information

- · A one-word postamble of all zero bits

Following each sector is a period of idle time that is simply a wait for the next sector pulse.

In addition to the data tracks, there are tracks both inside and outside of the data area that contain unique servo signals that define those areas as guard bands. If the read/write heads attempt to enter a guard band, the drive logic causes the positioner to retreat from the guard band and return to the data area.

The disk has a nominal rotational speed of 2400 rev/min. Therefore, the time for one revolution is 25 milliseconds. Since the revolution is divided into 40 sectors, the duration of each sector is 625 microseconds. This 625 microsecond period is divided into non-data (sector pulse, header, idle time) time and data time. The data time period is 500 microseconds. Thus, the data is transferred in 500 microsecond bursts that occur every 625 microseconds.

#### 1.6 RL01/RL02 SPECIFICATIONS

The following tables list the specifications of the RL01/RL02 drives and the RL01K/RL02K cartridges.

- Table 1-2 RL01/RL02 Disk Drive Physical and Environmental Specifications

Table 1-3 RL01/RL02 Disk Drive Operational Specifications

Table 1-4 RL01K/RL02K Disk Cartridge Specifications

#### Table 1-2 RL01/RL02 Disk Drive Physical and Environmental Specifications

| Characteristics          | Specifications                                                                                                                                                                                  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Width                    | Compatible with 19 inch RETMA rack                                                                                                                                                              |

| Depth                    | 63.5 cm (25 in) behind bezel                                                                                                                                                                    |

| Height                   | 26.52 cm (10.44 in)                                                                                                                                                                             |

| Weight                   | 34 kg (75 lb)                                                                                                                                                                                   |

| Mounting                 | The drive mounts on chassis slides                                                                                                                                                              |

| Power Source             | 90-127 Vac (47.5-63 Hz)<br>180-256 Vac (47.5-63 Hz)<br>(Manually selectable)                                                                                                                    |

| Input Power              | 160 W max at 115 Vac, 60 Hz                                                                                                                                                                     |

| Power Factor             | Greater than 0.85                                                                                                                                                                               |

| Starting Current         | 3.5A (rms) max @ 90 Vac/47.5-63 Hz<br>5.0A (rms) max @ 127 Vac/47.5-63 Hz<br>1.75A (rms) max @ 180 Vac/47.5-63 Hz<br>2.5A (rms) max @ 254 Vac/47.5-63 Hz                                        |

| Heat Dissipation         | 546 Btu/hr max                                                                                                                                                                                  |

| Power Cord and Connector | A molded line cord compatible with the drive operating voltage and the 861 power control for 120 Vac is attached to the drive. The power cord is 2.74 m (9 ft) long and the plug is NEMA 5-15P. |

|                          | The 230 Vac plug to be attached to high voltage drives is NEMA 6-15P.                                                                                                                           |

| Safety                   | The RL01/RL02 Disk Drive is UL listed and CSA certified.                                                                                                                                        |

| Interlocks               | Interlocks are used where potential exists for damage to drive, media, operators, or service personnel.                                                                                         |

### Table 1-2 RL01/RL02 Disk Drive Physical and Environmental Specifications (Cont)

| i nysicai ana Environmentai Specificationis (Cont.) |                                                                                                                                                                                                                 |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Characteristics                                     | Specifications                                                                                                                                                                                                  |  |

| Temperature/Humidity                                | Operating: Temperature: 10° C (50° F) to 40° C (104° F) Derate temperature at 1.8° C/1000 meters (1° F/1000 feet)                                                                                               |  |

|                                                     | Relative Humidity: 10 to 90 percent with maximum wet bulb temperature 28° C (82° F) and minimum dew point 2° C (36° F)                                                                                          |  |

|                                                     | Nonoperating:<br>Temperature: -40° C (-40° F) to 66° C (151° F)                                                                                                                                                 |  |

|                                                     | Relative Humidity: 10 to 95 percent, noncondensing                                                                                                                                                              |  |

| Altitude                                            | <b>Operating:</b> 2440 m (8,000 ft) max                                                                                                                                                                         |  |

|                                                     | Nonoperating: 9144 m (30,000 ft) max                                                                                                                                                                            |  |

| Shock                                               | <b>Operating:</b> Half sine shock pulse of gravity peak and $10 \pm 3$ ms duration applied once in either direction of three orthagonal axes (3 pulses total)                                                   |  |

|                                                     | Nonoperating:<br>Half sine shock pulses of 40 gravity peak and $30 \pm 10$ ms duration perpendicular to each of six package surfaces.                                                                           |  |

| Vibration                                           | Operating: Sinusoidal vibration (sweep rate 1 octave/min) 5-50 Hz, 0.002 in displacement amplitude 50-500 Hz, 0.25 gravity peak 500-50 Hz, 0.25 gravity peak 50-5 Hz, 0.002 in displacement amplitude           |  |

|                                                     | Nonoperating:<br>Vertical Axis Excitation – 1.40 gravity (rms) overall from 10 to 300 Hz;<br>power spectral density of 0.029 g <sup>2</sup> /Hz from 10 to 50 Hz, with 8 dB/octave<br>rolloff from 50 to 300 Hz |  |

|                                                     | Longitudinal and Lateral Axis Excitation – 0.68 gravity (rms) overall from 10 to 200 Hz; power spectral density of 0.007 g <sup>2</sup> /Hz from 10 to 50 Hz, with 8 dB/octave rolloff from 50 to 200 Hz        |  |

| EMI                                                 | Meets DEC Standard 102, Section 7.                                                                                                                                                                              |  |

| Dust                                                | The drive will operate in an ambient atmosphere of less than 5 million particles 0.5 microns or larger per cubic foot of air. The drive is intended to run in a light industry or cleaner environment.          |  |

| Attitude                                            | Maximum pitch: ± 15 degrees  Maximum roll: ± 15 degrees                                                                                                                                                         |  |

Table 1-3 RL01/RL02 Disk Drive Operational Specifications

| Characteristics     | Specifications                                                                                                                 |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|

| General             | Linear bit density: 147 bits/mm (3725 bits/in) at innermost track                                                              |

|                     | 16 bit words per sector: 128                                                                                                   |

|                     | Number of sectors per track: 40                                                                                                |

|                     | Track density: 4.9/mm (125/in) for RL01K, 9.8/mm (250/in) for RL02K Number of tracks per surface: 256 for RL01K, 512 for RL02K |

|                     | Number of surfaces: 2                                                                                                          |

|                     | Formatted capacity (megabytes): 5.2 for RL01K, 10.4 for RL02K Encoding method: Modified Frequency Modulation (MFM)             |

| Transfer Rate       | Bit rate: 4.1 megabits/second ± 1 percent                                                                                      |

| (Unbuffered Values) | Bit cell width: 244 ns ± 1 percent                                                                                             |

|                     | Word transfer rate (16 bit words): 256 kilowords/second $\pm$ 1 percent                                                        |

| Latency             | Rotational frequency: 2400 rev/min ± 0.25%                                                                                     |

| •                   | Average latency: 12.5 ms $\pm$ 0.25%                                                                                           |

|                     | Maximum latency: $25.0 \text{ ms} \pm 0.25\%$                                                                                  |

| Seek Time           | Average seek time: 55 ms max (85 tracks for RL01, 170 tracks for RL02)                                                         |

| 2001 2              | One cylinder/track seek time: 15 ms max                                                                                        |

|                     | Maximum seek time: 100 ms max (256 tracks for RL01, 512 tracks for RL02)                                                       |

| Start/Stop Time     | Start time: 45 seconds                                                                                                         |

|                     | Stop time: 30 seconds                                                                                                          |

| Data Format         | Refer to Figure 1-3                                                                                                            |

Table 1-4 RL01K/RL02K Disk Cartridge Specifications

| Characteristics                 | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Environment           | The cartridge will operate over a temperature range of 4° C to 48° C (40° F to 120° F), at a relative humidity of 8 to 80 percent. The wet bulb reading must be less than 25° C (78° F). Before a cartridge is placed in operation, it should be conditioned within its cover for a minimum of 2 hours in the same environment as that in which the disk drive is operating. (The above specified ranges do not necessarily apply to the disk drive). |

| Storage Environment             | The cartridge should be stored at a temperature between $-40^{\circ}$ C to $65^{\circ}$ C $(-40^{\circ}$ F to $150^{\circ}$ F), with a wet bulb reading not exceeding $29^{\circ}$ C $(85^{\circ}$ F). For wet bulb temperatures between $0.56^{\circ}$ C and $29^{\circ}$ C $(33^{\circ}$ F and $85^{\circ}$ F) the disk cartridge will withstand a relative humidity of 8 to 80 percent. The stray magnetic field intensity shall not exceed 50 Oe. |

| Dimensions (Cartridge)          | The external diameter of the top cover is 38.35 cm (15.1 in).                                                                                                                                                                                                                                                                                                                                                                                         |

|                                 | The external diameter of the protection cover is 37.03 cm (14.58 in).                                                                                                                                                                                                                                                                                                                                                                                 |

|                                 | The external height of the cartridge is 6.19 cm (2.44 in).                                                                                                                                                                                                                                                                                                                                                                                            |

| Maximum Speed                   | The rotating parts of the disk cartridge are capable of withstanding the effect of stress created while rotating at 2,500 rev/min.                                                                                                                                                                                                                                                                                                                    |

| Track Geometry                  | There are 256 discrete concentric tracks per data surface for the RL01K, 512 tracks per data surface for the RL02K.                                                                                                                                                                                                                                                                                                                                   |

| Identification of Data Location | Data Track Identification – Data tracks are numbered by consecutive decimal numbers (000-255, RL01K; 000-511, RL02K) starting at the outermost data track of each data surface.                                                                                                                                                                                                                                                                       |

|                                 | Data Surface Identification – The upper data surface is numbered 0 and the lower surface is numbered 1, to correspond with the head numbers.                                                                                                                                                                                                                                                                                                          |

|                                 | Cylinder Address – A cylinder is defined as both data tracks (on either surface) with a common data track identification.                                                                                                                                                                                                                                                                                                                             |

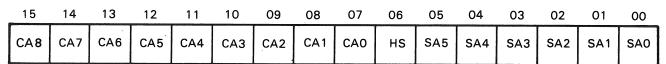

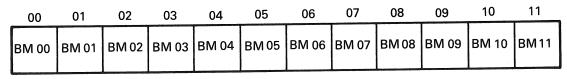

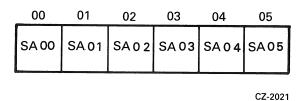

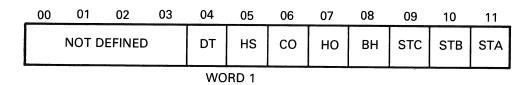

|                                 | Data Track Address – A 16-bit word defines the data track address. Bits 0-5 define the sector, bit 6 defines the surface, and bits 7-15 define the cylinder address. This information is in word 1 of each sector's header.                                                                                                                                                                                                                           |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# CHAPTER 2 INSTALLATION

#### 2.1 SITE PREPARATION AND PLANNING

This chapter describes power, space, environmental, cabling and safety requirements that must be considered before installation of the RL01/RL02 Disk Subsystem.

#### 2.1.1 Environmental Considerations

The RL01/RL02 Disk Subsystem is designed to operate in a business or light industry environment. Although cleanliness is an important consideration in the installation of any computer system, it is particularly crucial for proper operation of a disk drive. The RL01K-RL02K Disk Cartridge is not sealed while being loaded and is therefore vulnerable to dust or smoke particles suspended in the air, as well as fingerprints, hair, lint, etc. These minute obstructions can cause head crashes, resulting in severe damage to the read/write heads and disk surfaces.

- **2.1.1.1** Cleanliness The RL01/RL02 Disk Drives can operate in an ambient with less than one million particles per cubic foot of air which are 0.5 micron or larger in diameter. The drive contains a filter system which, under these conditions, maintains the particle count within the cartridge below 100 particles per cubic foot.

- **2.1.1.2** Space Requirements Provision should be made for service clearances of 1 m (36 in) at the front and rear of the rack or cabinet in which the drive is mounted and 1 m (36 in) at either side.

Storage space for the RL01K/RL02K cartridges should also be made available. Each cartridge has a diameter of approximately 38 cm (15 in) and a height of approximately 6 cm (2.5 in).

#### **CAUTION**

RL01K/RL02K Disk Cartridges must never be stacked on top of each other. A designated shelf area or specially designed disk cartridge storage unit is recommended (see the DIGITAL Supplies and Accessories Catalog).

- **2.1.1.3** Floor Loading The weight of the RL01/RL02 Disk Drive alone is 34 kg (75 lb), which will not place undue stress on most floors. However, the added weight of the rack or cabinet as well as the number of drives to be installed should be considered in relation to the weight of existing computer systems. Possible future expansion should also be a consideration.

- **2.1.1.4 Heat Dissipation** The heat dissipation of each RL01/RL02 Disk Drive is 546 Btu/hour maximum. The approximate cooling requirements for the entire system can be calculated by multiplying this figure by the number of drives, adding the result to the total heat dissipation of the other system components, and then adjusting the total figure to compensate for personnel, cooling system efficiency, etc. It is advisable to allow a safety margin of at least 25 percent above the maximum estimated requirements.

- **2.1.1.5** Acoustics Most computer sites require at least some degree of acoustical treatment. However, the RL01/RL02 Disk Subsystem should not contribute unduly to the overall system noise level. Ensure that acoustical materials used do not produce or harbor dust.

- **2.1.1.6** Temperature The RL01/RL02 Disk Subsystem will operate over a temperature range of  $10^{\circ}$  C ( $50^{\circ}$  F) to  $40^{\circ}$  C ( $104^{\circ}$  F). The maximum temperature gradient is  $16.6^{\circ}$  C ( $30^{\circ}$  F) per hour. The nonoperating temperature range is from - $40^{\circ}$  C ( $-40^{\circ}$  F) to  $66^{\circ}$  C ( $151^{\circ}$  F).

- **2.1.1.7 Relative Humidity** Humidity control is important for proper operation of any computer system since static electricity may cause memory errors or even permanent damage to logic components. The RL01/RL02 Disk Subsystem is designed to operate within a relative humidity range of 10 to 90 percent, with a maximum wet bulb temperature of 28° C (82° F) and a minimum dew point of 2° C (36° F). The nonoperating relative humidity range is from 10 to 95 percent, with a maximum wet bulb temperature of 46° C (115° F).

- **2.1.1.8** Altitude Computer systems operating at high altitudes may have heat dissipation problems. Altitude also affects the flying height of read/write heads in disk drives. The maximum altitude specified for operating the RL01/RL02 Disk Subsystem is 2440 M (8000 ft). Also, the maximum allowable operating temperature is reduced by a factor of 1.8° C per 1000m (1° F per 1000 ft) above sea level. Thus, the maximum allowable operating temperature at 2440 m (8000 ft) would be reduced to 36°C (96° F).

- **2.1.1.9** Power and Safety Precautions The RL01/RL02 Disk Subsystem presents no unusual fire or safety hazards to an existing computer system. AC power wiring should be checked carefully, however, to ensure that its capacity is adequate for the added load as well as for any possible expansion. The RL01/RL02 Disk Drive is UL listed and CSA certified.

- **2.1.1.10** Radiated Emissions Any source of electromagnetic interference (EMI) that is near the computer system may affect the operation of the processor and its related peripheral equipment. Common EMI sources that are known causes of failures include:

- Thunderstorms

- Broadcast stations

- Radar

- Mobile communications

- High-voltage power lines

- Power tools

- Arc welders

- Vehicle ignition systems

- Static electricity

The effect of radiated EMI emissions on a computer system is unpredictable. Thus, grounding plays an important role in protecting the circuits used in disk drive subsystems.

To help reduce the effects of known high-intensity EMI emissions perform the following actions:

- Ground window screens and other large metal surfaces.

- Ensure that the overall computer system is grounded properly (refer to Paragraph 2.1.5, Grounding Requirements).

- Provide proper storage (metal cabinets with doors) for disk cartridges.

**2.1.1.11 Attitude/Mechanical Shock** – Performance of the RL01/RL02 Disk Subsystem will not be affected by an attitude where maximum pitch and roll do not exceed 15 degrees.

The subsystem is designed to operate while a half-sine shock pulse of 10 gravity peak and  $10 \pm 3$  ms duration is applied once in either direction of three orthagonal axes (three pulses total).

2.1.2 Options

The RL01/RL02 Disk Drive can be shipped with various controllers (for Unibus, Omnibus and LSI-11 Bus computer systems), and can be configured for 115 Vac or 230 Vac operation.

Table 2-1 shows saleable RL01/RL02 subsystem options. Table 2-2 shows RL01/RL02 cabinet options.

Table 2-1 Saleable RL01/RL02 Subsystem Options

| Option<br>Number | Description                                                     |

|------------------|-----------------------------------------------------------------|

| RL01A            | RL01 unit, BC20J I/O cable, chassis slide and mounting hardware |

| RL02A            | RL02 unit, BC20J I/O cable, chassis slide and mounting hardware |

| RL01-AK          | RL01-A (drive), RL01K-DC (cartridge)                            |

| RL02-AK          | RL02-A (drive), RL02K-DC (cartridge)                            |

| RL01K-DC         | RL01 Data Cartridge                                             |

| RL02K-DC         | RL02 Data Cartridge                                             |

| RL11-AK          | RL01-AK, RL11 Controller, BC06R, terminator                     |

| RL211-AK         | RL02-AK, RL11 Controller, BC06R, terminator                     |

| RLV11-AK         | RL01-AK, RLV11 Controller, BC06R, terminator                    |

| RLV21-AK         | RL02-AK, RLV11 Controller, BC06R, terminator                    |

| RL8A-AK          | RL01-AK, RL8-A Controller, BC80J, terminator                    |

| RL28A-AK         | RL02-AK, RL8-A Controller, BC80J, terminator                    |

|                  |                                                                 |

Table 2-2 Saleable Cabinet Options: (Includes skins, doors, covers, trim, and power controllers)

| Type  | Volts      | Dwg                           | Remarks                                                                |

|-------|------------|-------------------------------|------------------------------------------------------------------------|

| H950  | 110        | H960-BC                       | Includes five 26.67 cm (10.5 in) high panels                           |

| H967  | 110<br>220 | H960-BD<br>H967-BA<br>H967-BB | 26.67 cm (10.5 in) cover panels (H950-QA) must be ordered if required. |

| H9500 | 110        | H9603-ED                      | SWLB with H9514-B top covers                                           |

|       | 220<br>110 | H9603-EE<br>H9601-ED          | DWLB with H9514-A top covers                                           |

|       | 220<br>110 | H9601-EE<br>H9602-EA          | SWHB complete hiboy cabinet                                            |

|       | 220<br>110 | H9602-EB<br>H9600-EA          | DWHB complete hiboy cabinet                                            |

| H9500 | 220        | H9600-EB<br>H9602-B-O         | SWHB option arrangement dwg. Order as required.                        |

|       |            | Н9600-А-О                     | DWHB option arrangement dwg. Order as required.                        |

|       |            | Н9603-В-О                     | SWLB option arrangement dwg. Order as required.                        |

| H9500 |            | Н9601-А-О                     | DWHB option arrangement dwg. Order as required.                        |

# Saleable Cable Options: Where an I/O cable length of more than 10 feet is required, order one of the following:

| Order No. | Part No.   | Length       |

|-----------|------------|--------------|

| BC20J-20  | 7012122-20 | 6 m (20 ft)  |

| BC20J-40  | 7012122-40 | 12 m (40 ft) |

| BC20J-60  | 7012122-60 | 18 m (60 ft) |

Total length of cable(s) from the controller to the last drive must not exceed 30 m (100 ft).

#### 2.1.3 AC Power Requirements

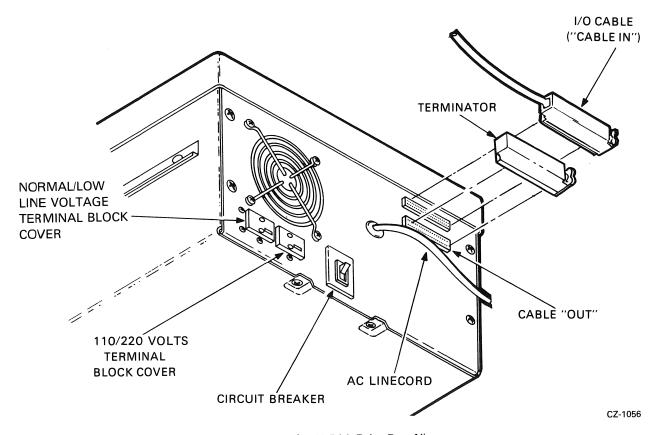

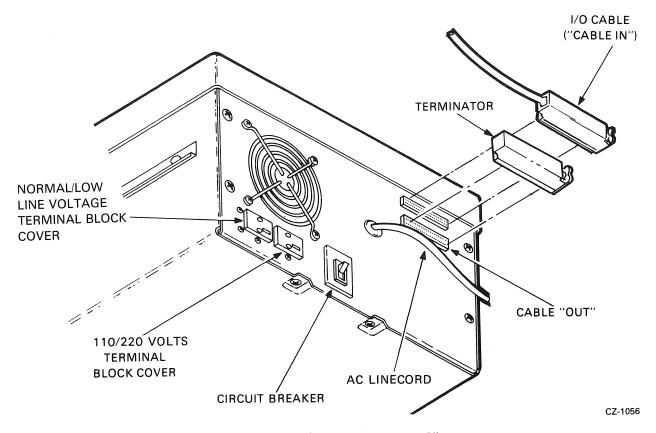

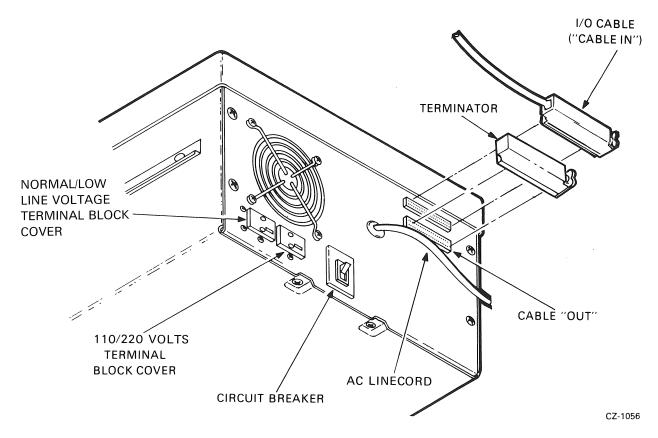

The RL01 or RL02 drive can operate within one of four voltage ranges that are manually selected by means of two terminal blocks located at the rear of the device (Figure 2-1). These voltage ranges are:

|     | 110     | 220     |

|-----|---------|---------|

| NOM | 100-120 | 200-256 |

| LO  | 90-105  | 180-210 |

The drive will operate when the line frequency is between 47.5 and 63 Hz.

Figure 2-1 RL01/RL02 Disk Drive-Rear View

**2.1.3.1** Standard Applications – The drive can be shipped from the factory as a free-standing unit or mounted in various racks and cabinets (refer to Paragraph 2.1.2, Options).

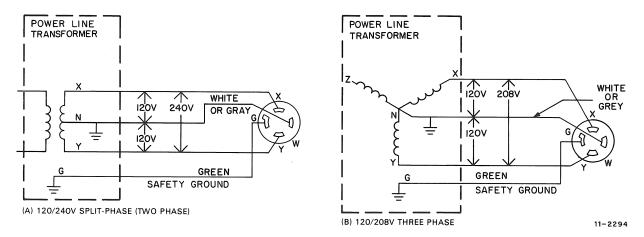

If shipped as a free-standing unit, the 2.74 m (9 ft) ac power cord is terminated with a NEMA type 5-15P plug (DIGITAL Part No. 90-08938). This plug requires a NEMA type 5-15R receptacle (Figure 2-2).

**2.1.3.2 Optional Applications** – Operation in the high voltage range (180-256 Vac) will require reconfiguring the terminal block at the rear of the drive and changing the line cord plug (Figure 2-1).

In 50 Hz applications, the line cord plug must be changed (Figure 2-2).

| SOURCE                                                               | PLUG                                                  | RECEPTACLE                     | USED ON                                                                                                             | ]                            |

|----------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------|

| 120V<br>15A<br>1-PHASE                                               | HUBBEL<br>#5266-C<br>NEMA # 5-15P<br>DEC # 90-08938   | #5262<br>5-15R<br>12-05351     | ALL 120 V TABLE-TOP COMPUTERS. STANDARD 120V LOW-CURRENT DISTRIBUTION. 120V TU10 UNITS. MOST 120V TERMINAL DEVICES. | POWER<br>CONTROLLER<br>861-F |

| 120/208V<br>30A<br>3-PHASE Y                                         | HUBBEL<br>#2611<br>NEMA # L6-30P<br>DEC # 12-11193    | #2610<br>L5-30R<br>12-11194    | ALL 120V STANDARD<br>CABINET MOUNTED EOPT                                                                           | POWER<br>CONTROLLER<br>861-C |

| 120/208-240V<br>20A<br>2-PHASE<br>or<br>120/208V<br>20A<br>3-PHASE Y | HUBBEL #2411 NEMA # L14-20P DEC # 12-11045            | #2410<br>L14-20R<br>12-11046 Y | 120V PDP-11/45 PRO-<br>CESSOR CABINET ONLY.                                                                         | POWER<br>CONTROLLER<br>861-A |

| 120/208V<br>20A<br>3-PHASE Y                                         | HUBBEL<br>#2511<br>NEMA # L21-20P<br>DEC # 12-11209 Z | #2510 W Z Z                    | 60 Hz RM 10 DRUM<br>60 Hz RP02/RP03/<br>RP04, RP05, RP06                                                            |                              |

| 240V<br>15A<br>1-PHASE                                               | NEMA # 6-15P<br>DEC # 90-08863                        | 6-15R<br>12-11204              | ALL 240V TABLE-TOP COMPUTERS. STANDARD LOW-CURRENT 240V DISTRIBUTION. MOST 240V TERMINAL DEVICES. 240V TU10.        |                              |

| 240V<br>20A<br>1-PHASE                                               | HUBBEL<br>#2321<br>NEMA # L6-20P<br>DEC # 12-11192    | #2320<br>L6-20R<br>12-11191    | ALL 240V STANDARD<br>CABINET MOUNTED<br>EQUIPMENT.                                                                  | POWER<br>CONTROLLER<br>861-B |

| 240/416V<br>20A<br>3-PHASE Y                                         | W X Y Y NEMA # NOT NEMA G DEC # 12-09010              | NOT NEMA<br>12-11259 G X       | 50 Hz RM10 DRUM<br>50 Hz RP02/RP03/<br>RP04                                                                         |                              |

| 120V<br>30A<br>1-PHASE                                               | HUBBEL 4 2811 NEMA L21-30P DEC 12-12314               | #2810<br>L21-30R<br>12-12315   | PDP11/70<br>PROCESSOR<br>PDP 11/70 MEM.<br>VAX-11/780<br>PROCESSOR                                                  | POWER<br>CONTROLLER<br>861-D |

CP-1968

Figure 2-2 Approved Electrical Plugs and Receptacles

#### 2.1.4 Installation Constraints

The route from the receiving area to the installation site that the equipment will travel should be studied in advance to ensure problem-free delivery. Among the considerations are:

- · Height and location of loading doors

- Size, capacity, and availability of elevators

- · Number and size of aisles and doors en route

- Bends or obstructions in hallways.

#### 2.1.5 Grounding Requirements

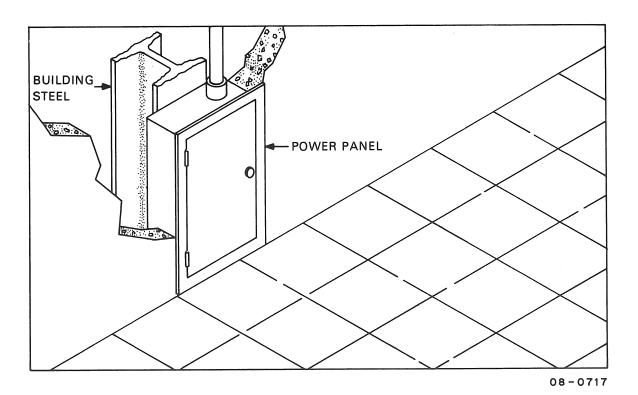

Each cabinet of a DIGITAL computer system is equipped with ground lug terminals that should be connected to a low-impedance earth ground by No. 4 AWG (5 mm/0.20 in) copper wire or stranded No. 4 AWG welding cable. A Burndy QA4C-B solderless lug (or equivalent) is recommended for terminating the cable. DIGITAL supplies a standard grounding conductor with each I/O and memory cabinet.

A steel building beam is an adequate ground in many instances. However, some disk-oriented systems may require additional connections to earth ground, in addition to the ground leads carried through various signal buses and ground connectors contained within the power cables. The green grounding wire in the power cable must also be returned to ground, usually through the conduit of the electrical distribution system. Note that the green wire is not a current-carrying conductor, nor a neutral conductor.

Whenever possible, the system power panel must be either mounted in contact with bare building steel by bonded joints (Figure 2-3) or connected to the steel by a short length of cable.

Figure 2-3 Power Panel Grounded To Building Frame

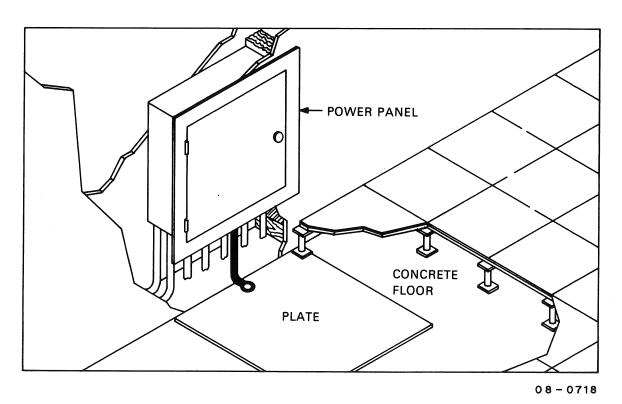

Where neither scheme is possible, a metal area (comprising the power panel, the conduit, and a metal plate) of at least 1 m<sup>2</sup> (10 ft<sup>2</sup>) that is in contact with masonry must be connected to the green ground wire (Figure 2-4). The connecting wire must not exceed 1.5 m (5 ft) in length and should be at least a No. 12 AWG (2mm).

When two cabinets are bolted together, DIGITAL bonds them electrically with a No. 4 AWG conductor (5 mm/0.20 in) or by several copper mesh straps connected between the cabinet frames.

After the grounding system is installed, it is advisable to take a voltage reading between the cabinet frame and the nearest grounded object. NBFU No. 70 (published by the National Bureau of Underwriters) provides further details regarding preferred grounding procedures.

Figure 2-4 Power Panel Grounded To Metal Plate

#### 2.2 AC CABLING

Computer equipment requires a power source with a minimum number of voltage and frequency disturbances. Line voltage disturbances greater than 1/4 cycle (measured at the receptacle during system operation) are undesirable.

DIGITAL power wiring conforms to Underwriters Laboratories, Inc., Handbook UL No. 478, National Electrical Code standards, and the type II requirements of the National Fire Protection Association (NFPA 70). This means that in the United States the wire used as equipment ground is green, or green with a yellow stripe; it carries no load current (except in emergency), but does carry leakage current. No equipment is permitted to leave DIGITAL that does not have a grounding connection to its frame.

The grounded conductor is light grey or white. It must not be used to ground equipment. Its purpose is to conduct current.

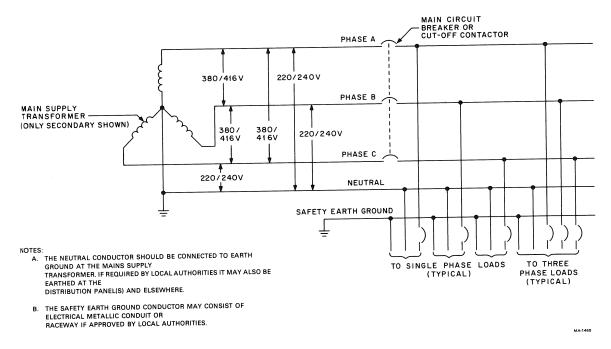

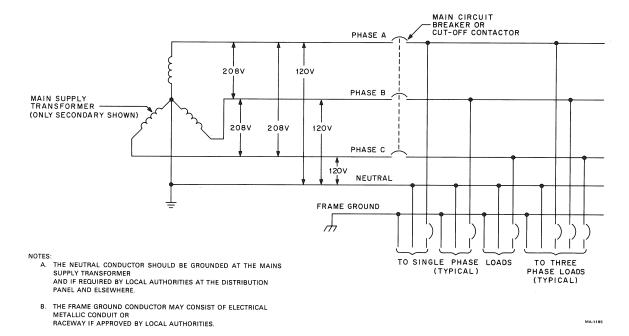

Lines 1, 2, and 3 in a typical 60 Hz power system (Figure 2-5) are represented by black, red, and blue wires, respectively, and phase rotation is in that order.

#### **CAUTION**

Where no grounded wire can be guaranteed, it must not be assumed. There are some 115 V/60 Hz systems within the United States where neither side of the line is grounded (115 V 3-phase delta).

Figure 2-5 Typical 60 Hz Power System

Figure 2-6 shows a typical 50 Hz power system.

Two types of power systems can be used to provide power to the NEMA type L14-20R receptacle. The type shown in Figure 2-7 is referred to as split-phase (or 2-phase 180 displaced) 120/240 Vac. It comprises a center-tapped transformer with 120 Vac between the center tap and either of the two legs. 240 Vac exists between the two outside legs.

The second type (Figure 2-8) is referred to as 3-phase Y (120 displaced) 120/280 Vac. The 120 Vac exists between neutral and any of the three other legs (X, Y, or Z), and 208 Vac exists between any two of the outer legs (i.e., between X and Y, X and Z, or Y and Z). Although Figure 2-8 shows the X and Y connections as the two phases used for the receptacle, any two of the three phases shown can be used.

The ground terminal on the L14-ZOR receptacle will normally have a green screw, the neutral terminal will be white or silver, and the "hot" terminal will be brass covered.

Figure 2-6 Typical 50 Hz Power System

Figure 2-7 Split Phase (2-phase) Power System

Figure 2-8 Three Phase Y Power System

#### 2.3 INSTALLATION - GENERAL

The controller should be installed first, followed by the drive(s). Next, the diagnostics should be run to demonstrate that the subsystem is functioning properly or to diagnose any problems. Paragraph 2.4 explains the installation of the RL11 Controller, Paragraph 2.5 deals with the RLV11 and Paragraph 2.6 describes RL8A installation.

Paragraph 2.7 contains instructions to install the unit and Paragraph 2.8 explains acceptance testing and contains separate paragraphs for each of the three controllers. Paragraph 2.9 describes the use of the M9312 bootstrap module that may be used on RL11-based systems.

#### 2.4 RL11 CONTROLLER INSTALLATION

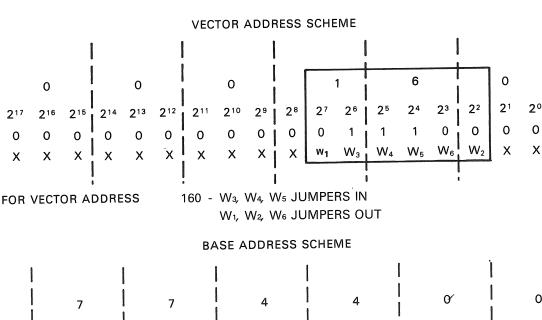

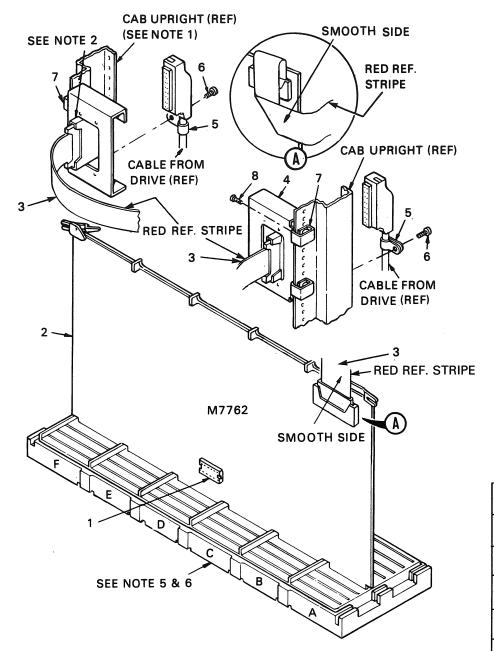

The RL11 Controller (M7762) is a single hex-height module that is installed in a hex-height SPC slot. Connector J1 connects the controller to the drive bus (Figure 2-9).

Of the 21 jumpers on the RL11 Controller, five are used for factory test purposes. The remaining 16 are for address selection:

W1-W6 VECTOR ADDRESS (160) W7-W16 BASE ADDRESS (774400)

#### NOTE

A logical one is represented by the presence of a jumper wire.

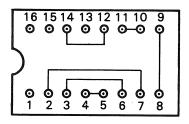

The Unibus priority plug sets the priority for bus requests. For the RL11 subsystem, bus requests are at priority level 5 (BR5/BG5). (See Figures 2-10 and 2-11.)

NOTE

Adjustments on the RL11 are preset at the factory and are not to be changed in the field.

FOR BASE ADDRESS 774400 - W<sub>12</sub>, W<sub>16</sub>, W<sub>7</sub> JUMPERS IN W<sub>1</sub>, W<sub>9</sub>, W<sub>10</sub>, W<sub>11</sub>, W<sub>13</sub>, W<sub>14</sub>, W<sub>15</sub>, JUMPERS OUT

#### NOTE:

X'S DENOTE DON'T CARE (NOT SELECTABLE)

1'S DENOTE JUMPER IN

O'S DENOTE JUMPER OUT

CZ-2004

Figure 2-10 RL11 Base And Vector Address Jumper Configuration

PRIORITY JUMPER PLUG FOR BUS REQUEST LEVEL FIVE (5)

| PLUG PIN NUMBER | SIGNAL NAME | UNIBUS PIN |

|-----------------|-------------|------------|

| 1               |             |            |

| 2               | BG IN       |            |

| 3               | BG OUT      |            |

| 4               | UB BG 4     | DT2        |

| 5               | UB BG 4 IN  | DS2        |

| 6               | UB BG 5     | DR2        |

| 7               | UB BG 5 IN  | DP2        |

| 8               | UB BG 6     | DN2        |

| 9               | UB BG 6 IN  | DM2        |

| 10              | UB BG 7     | DL2        |

| 11              | UB BG 7 IN  | DK2        |

| 12              | BR          |            |

| 13              | UB BR 4     | DD2        |

| 14              | UB BR 5     | DE2        |

| 15              | UB BR 6     | DF2        |

| 16              | UB BR 7     | DH2        |

MA-0560

Figure 2-11 RL11 Priority Jumper Assembly Connections

#### To install the controller:

- 1. Remove the M7762 module from its shipping container and examine it for any physical damage.

- 2. If a priority level other than 5 is required, obtain an appropriate priority jumper assembly or set up the priority jumper assembly (item 1, Figure 2-9) using Figure 2-11 as a guide. The vector and base address jumpers W1-W16 are for 160 and 774400, respectively. If the subsystem configuration requires other than standard addresses, set the jumpers up as shown in Figure 2-10. Physical location of these jumpers is shown on Figure 2-9.

- 3. Install the ribbon cable (BC06R-XX) with the red indicator stripe to the right and the smooth side facing the viewer when viewing the component side of the controller as shown in Figure 2-12. Dress the cable as necessary.

#### NOTES:

- 1. WHEN INSTALLED IN BA11K OR BA11L EXPANSION BOX, BC06R CABLE (ITEM #3) SHOULD BE FOLDED 90° AND ROUTED UP OUT OF THE BOX AS SHOWN.

- 2. WHEN ALTERNATE MOUNTING POSITION IS USED CONNECTOR IN TRANSITION BRACKET MUST BE INVERTED SO THAT I/O CABLE FROM DRIVE WILL HANG IN A DOWNWARD POSITION AS SHOWN.

- 3. ITEM #3 THRU ITEM #8 ARE NOT ASSEMBLED AT THIS POINT BUT ARE SHIPPED WITH UNIT FOR ASSEMBLY AT INSTALLATION TIME.

- 4. PRIORITY JUMPER ASSY (ITEM #1) TO BE PLUGGED INTO M7762 AT FINAL ASSY.

- 5. THE RL11 MODULE (M7762) WILL OCCUPY ONE HEX SPC SLOT.

- 6. JUMPER WIRE FROM CA1 TO CB1 ON THE SPC BACKPLANE MUST BE REMOVED AT INSTALLATION.

| DESCRIPTION                          | DWG PART NO.     | ITEM NO. |

|--------------------------------------|------------------|----------|

| 2 SCREW, PHL TRS HD. #10-32 × .50 LG | 9006073-03       | 8        |

| 2 NUT, SPRING #10-32                 | 9007786-00       | 7        |

| 1 SCREW, TAP-TLTE, #8 × .38 LG       | 9006418-01       | 6        |

| 1 CLAMP, CABLE                       | 9007083-00       | 5        |

| 1 TRANSITION BRACKET ASSY            | C-AD-7012415-0-0 | 4        |

| 1 CABLE ASSY                         | D-UA-BC06R-06    | 3        |

| 1 RL11 CONTROLLER                    | D-UA-M7762-0-0   | 2        |

| 1 PRIORITY JUMPER ASSY               | 5408778          | 1        |

CZ-2005

Figure 2-12 RL11 Controller Installation

|   | ₹ |  |  |

|---|---|--|--|

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

| • |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

4. Insert the controller into its appropriate slot in the SPC backplane as shown in Figure 2-12 after ensuring that the slot does not contain a grant continuity module in row D. Do not chafe the ribbon cable. Route the cable up and out to the rear of the cabinet, allowing for cable strain relief.

#### NOTE

# See Appendix A for configuration rules and SPC slot selection considerations.

- 5. Remove the jumper between CA1 and CB1, (NPR Grant) on the backplane, if the jumper exists.

- 6. Install the transition bracket at the rear of the cabinet shown in Figure 2-12. Assemble and install transition connector.

- 7. Connect the other end of the ribbon cable (BC06R-XX) with the red indicator stripe on the top. Use Figure 2-12 as a guide.

- 8. Apply system power and, using a suitable measuring device (i.e., digital voltmeter or equivalent), verify the voltages are within the ranges specified below.

| VOLTAGE                                | RANGE                                                              | TEST POINT               |                       |

|----------------------------------------|--------------------------------------------------------------------|--------------------------|-----------------------|

| GROUND<br>+5 VDC<br>+15 VDC<br>-15 VDC | +4.75 TO +5.25 VDC<br>+14.25 TO +15.75 VDC<br>-15.75 TO -14.25 VDC | AC2<br>AA2<br>CV1<br>CB2 | BACKPLANE<br>LOCATION |

Measure all voltages between the ground test point and the appropriate voltage test point. If any adjustments to the power supply are necessary, refer to the appropriate manual.

#### 2.5 RVL11 CONTROLLER INSTALLATION

An RLV11 Controller is comprised of a bus interface module (M8014) and the drive bus module (M8013). Each module has switches, jumpers, trimpots, and connectors that are explained in the following paragraphs.

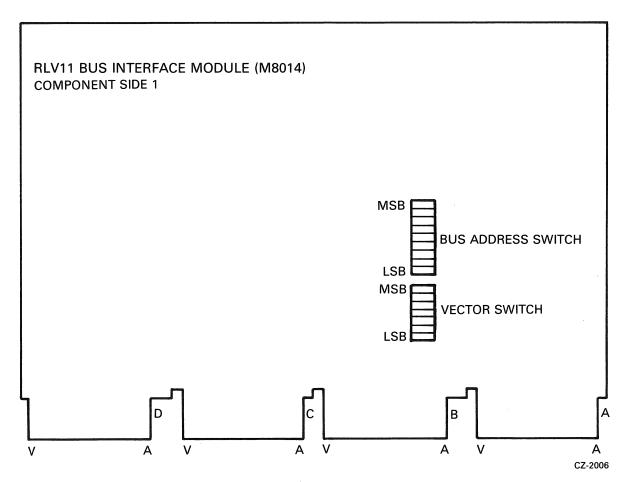

#### 2.5.1 Bus Interface Module

The bus interface module (M8014) contains the logic circuits that perform the following major functions:

- LSI-11 bus interface functions

- Programmable registers

- Silo data storage and control circuits

An illustration of the component side of M8014 is shown in Figure 2-13. The location of the bus address switches, the vector address switches, and the connector finger assignments are shown in this figure.

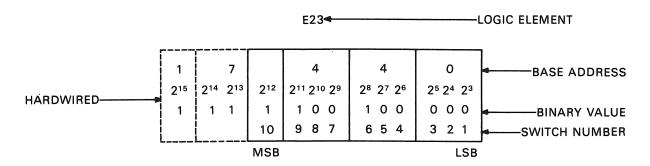

The bus address switch is used to set up the device base address. It is normally factory preset to 7440. This means the device CS register has an address of 174400 and the MP register has an address of 174406. The switches have the ON and OFF positions labeled. The ON position is the logical 1 or true state (Figure 2-14).

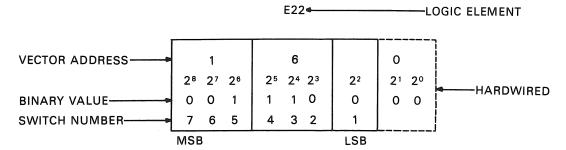

The vector address switch is used to select the address of the vector for this device when it interrupts. It is factory preset for an address of 160 (Figure 2-15).

2-16

Figure 2-13 RLV11 Bus Interface Module (M8014) (Component Side)

FOR EACH "0" SET THE CORRESPONDING SWITCH "OFF"

FOR EACH "1" SET THE CORRESPONDING SWITCH "ON"

USE THIS SCHEME TO SELECT THE APPROPRIATE BASE ADDRESS IF A DIFFERENT BASE ADDRESS IS REQUIRED

CZ-2034

Figure 2-14 RLV11 Base Address Switch Settings

FOR EACH "O" SET THE CORRESPONDING SWITCH "OFF"

FOR EACH "1" SET THE CORRESPONDING SWITCH "ON"

USE THIS SCHEME TO SELECT THE APPROPRIATE VECTOR ADDRESS IF A DIFFERENT VECTOR ADDRESS IS REQUIRED

CZ-2007

Figure 2-15 RLV11 Vector Address Switch Settings

#### 2.5.2 Drive Module

The drive module (M8013) contains the circuitry that performs the following major functions:

- Data formatting and error detecting circuits

- Control microsequencer and timing circuits

- Drive bus interface

An illustration of the component side of M8013 is shown in Figure 2-16.

# NOTE Adjustments to the RLV11 are preset at the factory and are not to be adjusted in the field.

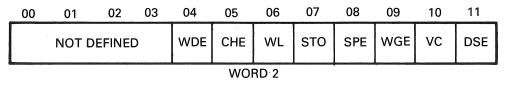

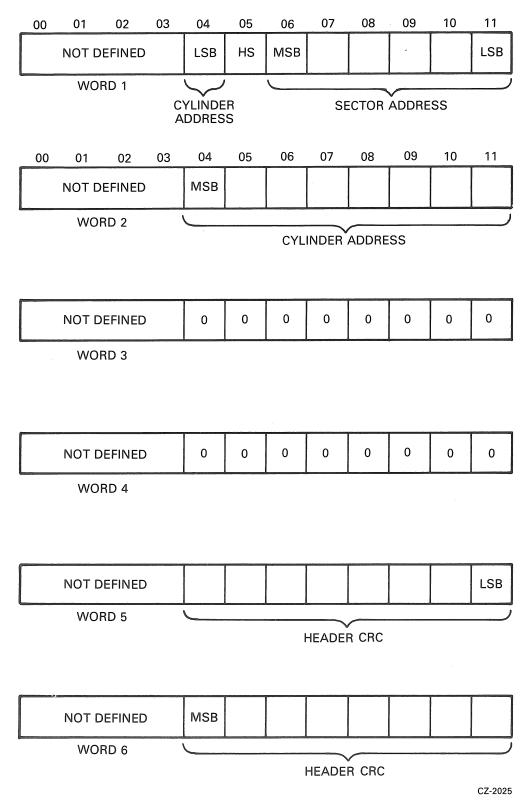

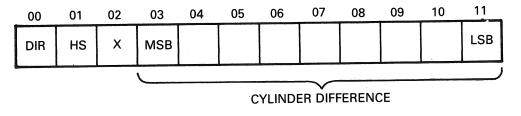

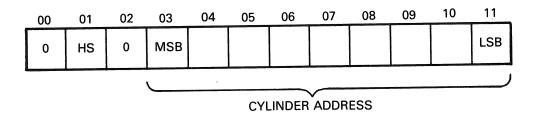

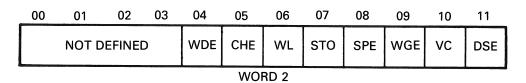

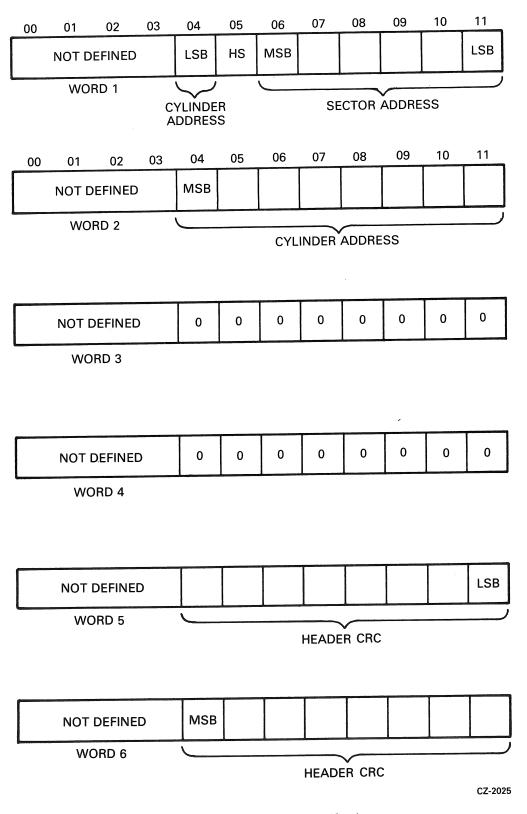

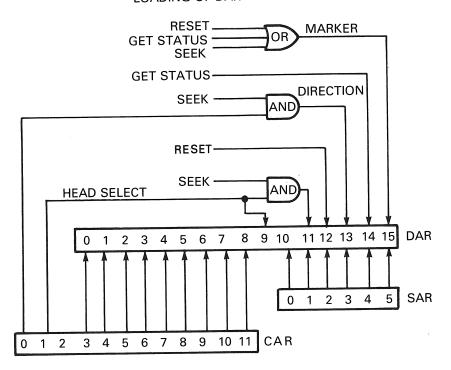

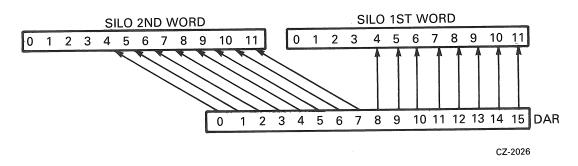

#### 2.5.3 Module Slot Location