## **DEC LANcontroller 400 Installation Guide**

Order Number: EK-DEMNA-IN-001

The DEC LANcontroller 400 adapter (also known as the DEMNA controller) is an Ethernet/802 controller for systems that have an XMI bus. This guide is intended for use by Digital customer service representatives and self-maintenance customers.

digital equipment corporation maynard, massachusetts

#### First Printing, April 1990

The informs ion in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright @1990 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEBNA PDP VAXcluster

DEC ULTRIX VAXELN

DEC LANcontroller UNIBUS VMS

DECnet VAX XMI

DECUS VAXBI digital

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

|      | PREF   | ACE                                              | lx   |

|------|--------|--------------------------------------------------|------|

| СНАР | TER 1  | DEC LANCONTROLLER 400 MODULE OVERVIEW            | 11   |

|      | 1.1    | BASIC FUNCTIONS                                  | 1-1  |

|      | 1.2    | LOGIC OVERVIEW                                   | 1-3  |

|      |        | 1.2.1 Microprocessor Subsystem                   |      |

|      |        | 1.2.2 Shared Memory Subsystem                    |      |

|      |        | 1.2.3 Ethernet Interface Subsystem               |      |

|      |        | 1.2.4 XMI Interface Subsystem                    | 1-6  |

|      | 1.3    | PHYSICAL DESCRIPTION                             | 1-7  |

|      |        | 1.3.1 Cabinet Kits                               | 1-8  |

|      |        | 1.3.2 Status LEDs                                |      |

| CHAP | 71EH 2 | INSTALLATION                                     | 2–1  |

|      | 2.1    | HARDWARE INSTALLATION                            | 2-1  |

|      |        | 2.1.1 Hardware Installation in a VAX 6000 System |      |

|      |        | 2.1.2 Hardware Installation in a VAX 9000 System | 2-7  |

|      | 2.2    | VERIFICATION OF HARDWARE INSTALLATION            | 2–14 |

|      | 2.3    | VERIFICATION OF DEMNA OPERATION IN NETWORK       | 2-15 |

|      | 2.4    | INTERNAL ETHERNET CABLE                          | 2–16 |

|      | 2.5    | EXTERNAL TRANSCEIVER CABLE                       | 2-19 |

|      | 2.6    | INTERNAL CABLE FOR PHYSICAL CONSOLE              | 2–19 |

|      | 2.7    | REMOVAL                                                                                                                                                                                                                         | 2-22                                              |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| СНАР | TER 3  | POWER-UP SELF-TEST                                                                                                                                                                                                              | 3–1                                               |

|      | 3.1    | HOW TO RUN SELF-TEST                                                                                                                                                                                                            | 3–1                                               |

|      | 3.2    | REPORTING SELF-TEST RESULTS                                                                                                                                                                                                     | 3–3                                               |

|      |        | 3.2.1 Self-Test Results in LEDs  3.2.2 Self-Test Results in the Power-Up Diagnostic Register                                                                                                                                    | 3–3<br>3–3                                        |

|      | 3.3    | INTERPRETING TEST RESULTS                                                                                                                                                                                                       | 3–4                                               |

|      | 3.4    | TESTED COMPONENTS                                                                                                                                                                                                               | 3–5                                               |

|      | 3.5    | UNTESTED COMPONENTS AND FUNCTIONS                                                                                                                                                                                               | 3–5                                               |

| APPE | NDIX A | ENVIRONMENTAL REQUIREMENTS                                                                                                                                                                                                      | <b>A-1</b>                                        |

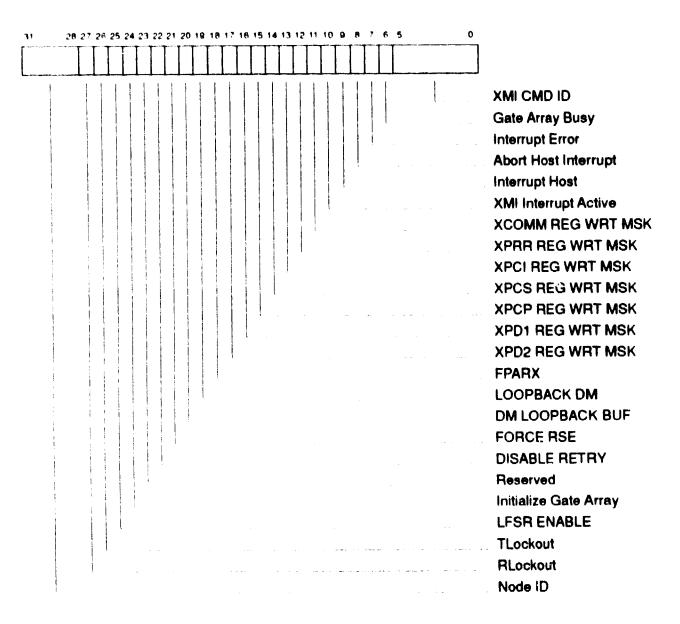

| APPE | NDIX B | REGISTERS  DEVICE REGISTER (XDEV)  BUS ERROR REGISTER (XBER)  POWER-UP DIAGNOSTIC REGISTER (XPUD)  FAILING ADDRESS REGISTER (XFADR)  FAILING ADDRESS EXTENSION REGISTER (XFAER)  GATE ARRAY CONTROL AND STATUS REGISTER (GACSR) | B-1<br>B 3<br>B-6<br>B-16<br>B-25<br>B-28<br>B-32 |

| APPE | NDIX C |                                                                                                                                                                                                                                 | C_1                                               |

| APPENDIX | D HOW TO MODIFY FLAGS IN EEPROM                    | D-1         |

|----------|----------------------------------------------------|-------------|

| APPENDIX | E DEVICE TYPE CODES FOR XMI MODULES                | E-1         |

| APPENDIX | F ETHERNET PROTOCOL TYPES                          | F-1         |

| APPENDIX | G ETHERNET ADDRESSES                               | G-1         |

| APPENDIX | H SAP ASSIGNMENTS AND SNAP PROTOCOL ID ASSIGNMENTS | H-1         |

| APPENDIX | HOW TO READ THE DEMNA ETHERNET ADDRESS             | <b>I</b> —1 |

| 1.1      | SYSTEMS WITH DECNET                                | 1-1         |

| 1.2      | FROM THE CONSOLE MONITOR PROGRAM                   | I-1         |

| 1.3      | VAX 6000 SYSTEM                                    | 1-2         |

| 1.4      | VAX 9000 SYSTEM                                    | 1-3         |

|          |                                                    |             |

INDEX

| EXAM  | PLES         |                                                                |

|-------|--------------|----------------------------------------------------------------|

|       | 3-1          | Running Self-Test on a VAX 6000 System                         |

|       | 3-2          | Running Self-Test on a VAX 9000 System                         |

|       | <b>I–1</b>   | Examining the DEMNA DPA from the DEMNA Console Monitor Program |

|       | I-2          | Examining the DEMNA DPA on a VAX 6000                          |

|       | I <b>-</b> 3 | Examining the DEMNA DPA on a VAX 9000                          |

| FIGUR | ES           |                                                                |

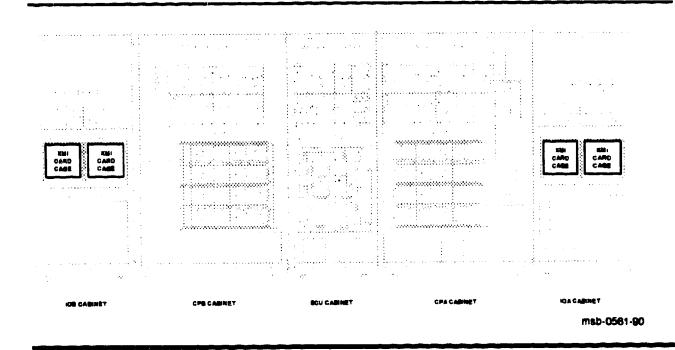

|       | 1-1          | DEMNA Module in an XMI System                                  |

|       | 1-2          | DEMNA Simplified Block Diagram                                 |

|       | 2-1          | Location of XMI Card Cage in a VAX 6000 System                 |

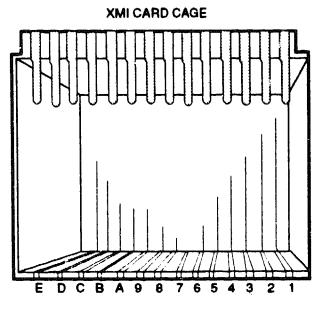

|       | 2-2          | XMI Card Cage Slots                                            |

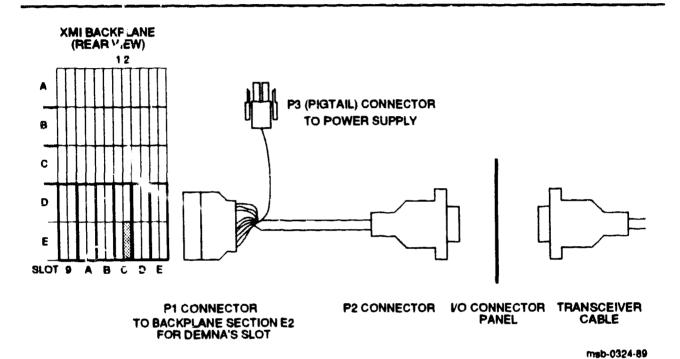

|       | 2-3          | Internal Ethernet Cable Connections                            |

|       | 2-4          | System Interconnect Panel—VAX 6000 Model 400 System            |

|       | 2-5          | Internal Cable for Physical Console                            |

|       | 2–6          | Location of XMI Card Cage in a VAX 9000 Model 2xx System       |

|       | 2-7          | Location of XMI Card Cages in a VAX 9000 Model 4xx System      |

|       | 2-8          | XMI Card Cage                                                  |

|       | 2-9          | Internal Ethernet Cable Connections                            |

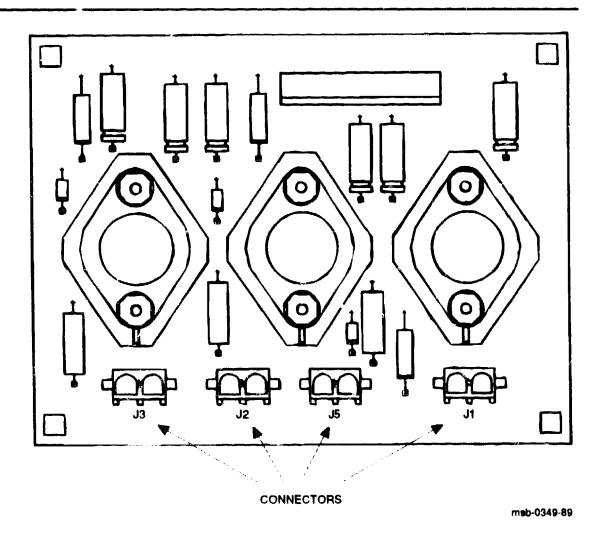

|       | 2-10         | Power Distribution Adapter—VAX 9000 Systems                    |

|       | 2-11         | Internal Cable for Physical Console                            |

|       | 2-12         | P1 Connector Pinouts of Internal Ethernet Cable                |

|       | 2-13         | P2 Connector Pinouts of Internal Ethernet Cable                |

|       | 2-14         | P1 Connector Pinouts of Internal Cable for Physical Console    |

|       | 2-15         | P2 Connector Pinouts of Internal Cable for Physical Console    |

|       | 3–1          | LFD Locations                                                  |

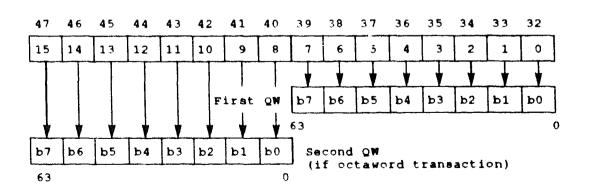

|       | B-1          | Mask Field Bit Assignments                                     |

| TAE | BLES        |                                                             |

|-----|-------------|-------------------------------------------------------------|

|     | 1-1         | Packing List for DEMNA Option                               |

|     | 1-2         | Cabinet Kits for DEMNA Options                              |

|     | 2-1         | Power Connection for Internal Ethernet Cable                |

|     | 2-2         | P1 Connector Pinouts of Internal Ethernet Cable             |

|     | 2-3         | P2 Connector Pinouts of Internal Ethernet Cable             |

|     | 2-4         | P1 Connector Pinouts of Internal Cable for Physical Console |

|     | 2-5         | P2 Connector Pinouts of Internal Cable for Physical Console |

|     | B-1         | Registers Useful During Installation—Summary                |

|     | B-2         | Abbreviations for Bit Types                                 |

|     | <b>B</b> -3 | Example of Device Revision Field                            |

|     | D-1         | EEPROM Flags                                                |

|     | D-2         | Distribution Media for EVGDB                                |

|     | E-1         | Device Type Codes for XMI Modules                           |

|     | F-1         | Cross-Company Ethernet Protocol Type                        |

|     | F-2         | Digital's Ethernet Protocol Types                           |

|     | G-1         | Cross-Company Multicast Addresses                           |

|     | G-2         | Digital's Multicast Addresses                               |

|     | G-3         | Digital's Physical Addresses                                |

|     | G-4         | Other Physical Addresses                                    |

|     | H-1         | Cross-Company SAP Assignments                               |

|     | H-2         | Digital's SNAP Protocol IDs                                 |

## **Preface**

## **Purpose of This Manual**

This manual describes how to install the DEC LANcontroller 400 adapter. The DEC LANcontroller 400 provides an interface between an Ethernet/IEEE 802 local area network and a system that has an XMI bus.

This manual also describes the adapter's self-test and gives advice for troubleshooting.

The DEC LANcontroller 400 is also known as the DEMNA controller. Throughout the rest of this manual, the DEC LANcontroller 400 is referred to as the DEMNA.

## **Intended Audience**

This manual is for Digital and customer personnel who install or replace the DEMNA in the field.

#### **Document Structure**

This munual has three chapters and nine appendixes, which are described below:

Chapter 1 briefly describes the DEMNA module, its functions, its logic, and what you should have received.

Chapter 2 describes installation of the module.

Chapter 3 describes the DEMNA self-test and how to interpret the results.

Appendix A gives environmental requirements for the DEMNA module.

Appendix B gives register information.

Appendix C describes how to convert an Ethernet address to a DECnet address.

Appendix D describes three customer-modifiable flags in DEMNA EEPROM and indicates how to modify the flag settings.

#### Preface

Appendix E lists the device type codes of all XMI modules available at the printing of this manual.

Appendix F lists some commonly used Ethernet protocol types.

Appendix G lists some commonly used multicast addresses.

Appendix H lists some commonly used 802 SAPs and SNAP SAP protocol IDs.

Appendix I describes how to read the DEMNA Ethernet address.

#### **Associated Documents**

Related documentation includes:

- DEC LANcontroller 400 Console User's Guide, EK-DEMNA-UG

- DEC LANcontroller 400 Programmer's Guide, EK-DEMNA-PG

- DEC LANcontroller 400 Technical Manual, EK-DEMNA-TM

- Ethernet Installation Guide, EK-ETHER-IN

- VAX 9000 Family System Maintenance Guide, Vol. 2, EK-KA902-MG

- VMS Network Control Program Manual, AA-LA50A-TE

#### Conventions Used

- All addresses are in hexadecimal (hex). All bit patterns are in binary notation. All other numbers are decimal unless otherwise indicated.

- Ranges are inclusive. For example, the range 0-4 includes the integers 0, 1, 2, 3, 4.

- Bits are enclosed in angle brackets (for example, <12>).

- Bit ranges are indicated by two bits in descending order separated by a colon; for example, <12:1>. Bit ranges are inclusive.

- K = kilo (1024); M = mega (1024\*\*2); G = giga (1024 \*\*3).

- The term "asserted" indicates that a signal line is in the true state.

The term "deasserted" indicates that a signal line is in the false state.

- "Assertion" is the transition from the false to the true state.

- "Deassertion" is the transition from the true to the false state.

## **Command Notation**

The following command notation is used in this manual:

| Convention                  | Meaning                                                                                                                                                                                                                     |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| { }                         | Large braces enclose lists from which you must choose one item. For example: { KERNEL } USER                                                                                                                                |

|                             | Horizontal ellipsis points mean that you can repeat the item preceding the points. For example: /qualifier                                                                                                                  |

| · .                         | Horizontal or vertical ellipsis points in an example indicate that not all the information the system would display is shown or that not all the information a user is to supply is shown.                                  |

| <b>{ }</b>                  | Braces followed by a comma and horizontal ellipsis points mean that you can repeat the enclosed items one or more times, separating two or more items with commas.                                                          |

|                             | Square brackets enclose items you can omit. For example: [ =option, ]                                                                                                                                                       |

| UPPERCASE characters        | Language-specific reserved words and identifiers are printed in uppercase characters. However, you can enter them in uppercase, lowercase, or a combination of uppercase and lowercase characters.                          |

| italic lowercase characters | Elements you must replace according to the description in the text are printed in italic lowercase characters. However, you can enter them in lowercase, uppercase, or a combination of lowercase and uppercase characters. |

## DEC LANcontroller 400 Module Overview

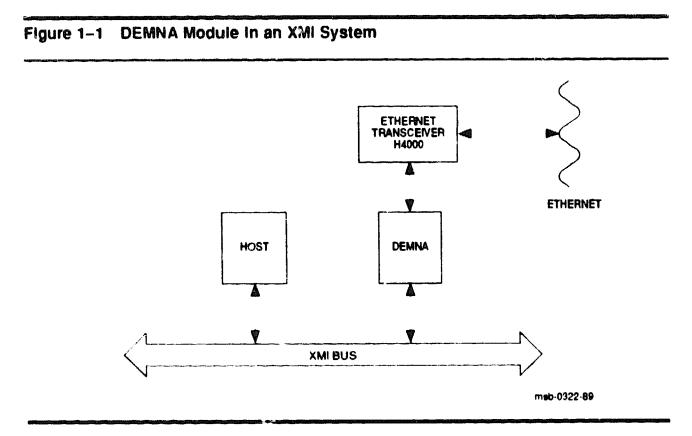

The DEC LANcontroller 400 is an intelligent, high-performance I/O controller that enables a host processor on the XMI bus to communicate with other nodes in an Ethernet/802 local area network. The DEC LANcontroller 400 is compatible with the Ethernet and IEEE 802 specifications. Digital's Systems and Options Catalog indicates which systems support the DEMNA option.

A single XMI bus can support multiple DEC LANcontroller 400s. An XMI bus can thus connect to multiple Ethernet/802 networks. Each DEC LANcontroller 400 connects to a single network through a standard 15-pin Sub-D connector.

The DEC LANcontroller 400 is also called the DEMNA controller. Throughout the rest of this manual, the DEC LANcontroller 400 is referred to as the DEMNA.

#### 1.1 BASIC FUNCTIONS

The DEMNA supports one Ethernet/IEEE 802 port, which provides the physical link layer and portions of the data link communication layer of the Ethernet and 802 protocols, as defined by the Ethernet and IEEE 802 specifications.

With its own onboard CVAX processor, the DEMNA can control operations independently of the host processor. The details of Ethernet transactions, including data transfer over the XMI bus, are thus transparent to the host processor (see Figure 1-1).

The onboard firmware is contained in EEPROM, which allows revised firmware to be loaded without hardware modification. The firmware can thus be easily upgraded in the field. In addition, various DEMNA operating parameters can be modified easily in the field.

<sup>&</sup>lt;sup>1</sup> In this manual, 802 refers specifically to the CSMA/CD local area network defined in the IEEE 802.2 and 802.3 specifications (physical and data link layers).

The DEMNA firmware includes a console monitor program that allows a user at virtually any terminal on the network to monitor DEMNA operation and network traffic. The console monitor program can be accessed over the network or from a terminal (called the physical console) attached directly to the DEMNA. (See the DEC LANcontroller 400 Console User's Guide, DEC LANcontroller 400 Technical Manual, or the DEC LANcontroller 400 Programmer's Guide for a description of the console monitor program.)

The DEMNA has extensive onboard tests. On power-up or reset, the DEMNA tests itself and makes its status (pass or fail) available through LEDs on the module and through an onboard Power-Up Diagnostic (XPUD) Register. In addition, a customer service engineer may invoke other onboard diagnostics from the system console or the DEMNA physical console to test the DEMNA's logic and functionality more extensively.

The DEMNA may participate in network boot operations. The DEMNA may be specified as the boot device by its host system or be enabled to involuntarily boot its host system on receiving a valid Boot message over

the network. (See the DEC LANcontroller 400 Technical Manual for further information.)

## 1.2 LOGIC OVERVIEW

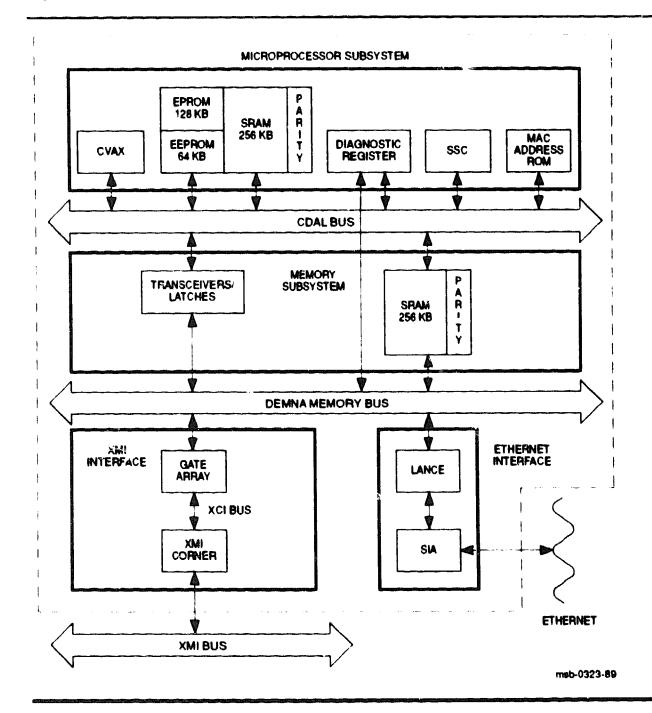

The DEMNA logic is divided into the following four subsystems, as shown in Figure 1-2:

- Microprocessor subsystem

- Shared memory subsystem

- XMI interface subsystem

- Ethernet interface subsystem

## 1.2.1 Microprocessor Subsystem

The microprocessor subsystem performs the following major functions:

- Stores and executes the module firmware, including onboard diagnostics and the console monitor program

- Stores and supplies the module's default (MAC) Ethernet address

The microprocessor subsystem contains the following major components:

- CVAX—a 32-bit CMOS processor dedicated to running firmware. The CVAX cannot be used directly by application programs running on the host processor or by a user at the system console.

- System Support Chip (SSC)—This chip provides control logic for the microprocessor subsystem, including timers, address decode logic, internal processor registers, and a UART for connection with the DEMNA physical console.

- EEPROM and CVAX RAM—The EEPROM stores the module's operational firmware, which executes from CVAX RAM (SRAM).

The EEPROM also stores history data on DEMNA failures and errors.

Figure 1-2 DEMNA Simplified Block Diagram

- MAC Address (ENET) PROM—This PROM stores the module's default physical (Ethernet) address (DPA),<sup>1</sup> which is also called the Medium Access Control (MAC) address. The PROM also stores a PROM test pattern.

- EPROM—The EPROM stores a working copy of the DEMNA firmware minus the console monitor program. If the DEMNA self-test finds that the EEPROM contents are invalid, the EPROM code is loaded into CVAX RAM so that diagnostics can be executed.

- Diagnostic Register—This register is a control/status register that controls certain low-level diagnostic operations, such as the disabling of CVAX RAM parity.

The CVAX, SSC, CVAX RAM, and Diagnostic Register connect to each other through the CDAL bus, which in turn connects to the DEMNA memory bus through latched transceivers.

## 1.2.2 Shared Memory Subsystem

The shared memory subsystem performs the following major functions:

- Buffers packets to and from the Ethernet interface

- Buffers transfers to and from the XMI bus

- Stores shared data structures that allow the CVAX and LANCE to communicate

The shared memory subsystem has the following major components:

- 256 Kbytes of parity-protected SRAM—The SRAM buffers Ethernet and XMI transfers and stores data structures shared by the CVAX and LANCE.

- Bus control logic—This logic controls read/write timing and read/write signals.

- DMA logic—This logic controls access to the SRAM.

- DEMNA timeout logic—This logic detects when a DMA grant on the DEMNA memory bus has been outstanding longer than the timeout period.

<sup>&</sup>lt;sup>1</sup> At the request of applications starting up a protocol such as DECnet, the port driver may assign one or more alternative addresses to the DEMNA. This type of address is called an actual physical address (APA).

The SRAM is on the DEMNA memory bus, which connects to the Ethernet interface, XMI interface, and the CDAL bus. The SRAM can be accessed by the LANCE chip (Ethernet interface), CVAX, or DEMNA gate array (XMI interface). The DMA access priority for these devices is LANCE, CVAX, and gate array.

## 1.2.3 Ethernet Interface Subsystem

The Ethernet interface provides an interface between the DEMNA's shared memory and the Ethernet wire. The Ethernet interface performs transmits (reads) from the shared memory and receives (writes) to the shared memory.

The Ethernet interface has the following major components:

- Local Area Network Controller for Ethernet (LANCE) chip—The LANCE chip implements the microprocessor interface, performs DMA to and from the DEMNA shared memory, implements the CSMA/CD network access algorithm, does packet handling on transmits and receives, and reports errors.

- Serial Interface Adapter (SIA) chip—The SIA chip performs

Manchester encoding for transmits, Manchester decoding for receives,

and implements a TTL/differential signal interface between the

LANCE (TTL) and the Ethernet wire (differential signals).

- Bus interface logic—This logic generates byte parity on transfers to DEMNA shared memory and checks byte parity on transfers from shared memory.

## 1.2.4 XMI Interface Subsystem

The XMI interface provides an interface between the DEMNA's shared memory and the XMI bus. The XMI interface performs the following major functions:

- Transfers Ethernet read and write data between DEMNA shared memory and host memory

- Performs control operations for the DEMNA CVAX (high-priority quadword XMI reads and writes to memory and longword XMI I/O reads and writes)

- Implements the DEMNA port registers

- Implements the XMI-required registers

Implements XMI interrupt logic

The XMI interface has the following major components:

- Gate array—The gate array implements most of the XMI interface logic.

- XMI resistors, clocks, and module-decoupling capacitors.

- XMI timeout logic—This logic detects timeouts for XMI operations.

## 1.3 PHYSICAL DESCRIPTION

The DEMNA option consists of a single board. The DEMNA has the following two cables:

- An internal Ethernet cable that connects the DEMNA with the transceiver cable and provides power to an H4000 transceiver (Section 2.4). This cable is not part of the DEMNA option but is included in the cabinet kits for the DEMNA.

- An internal cable for the physical console that connects the DEMNA with a terminal cable. This cable has its own cabinet kit.

An external Ethernet cable runs from the bulkhead to an Ethernet transceiver. This cable is not part of the DEMNA option and is not included in the cabinet kits for the DEMNA. The cable must be ordered separately. (See Digital's Systems and Options Catalog for more information.)

Table 1-1 lists the items on the DEMNA packing list. These are the items included with the DEBNI option (DEMNA-M).

| Table 1- | 1 Packing | List for | <b>DEMNA</b> | Option |

|----------|-----------|----------|--------------|--------|

|----------|-----------|----------|--------------|--------|

| Part Number | Quantity | Description                                |

|-------------|----------|--------------------------------------------|

| T2020       | 1        | DEMNA module                               |

| EK-DEMNA-IN | 1        | DEC LANcontroller 400 Installation Guide   |

| EK-DEMNA-RM | 1        | DEC LANcontroller 400 Release Note         |

| EK-DEMNA-UG | 1        | DEC LANcontroller 400 Console User's Guide |

#### 1.3.1 Cabinet Kits

Table 1-2 lists DEMNA cabinet kits for VAX 6000 and 9000 systems. Cabinet kits must be ordered separately from the DEMNA option. For new systems not included in this table, please see Digital's Systems and Options Catalog.

Table 1-2 Cabinet Kits for DEMNA Options

| Description                                  | Kit Number  | Contents                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Internal<br>Cable for<br>Physical<br>Console | CK-DEMNA-AM | I/O connector panel for VAX 6000 cabinets (74-26407-32) I/O connector panel for VAX 9000 cabinets (70-28010-01) Blank panel for I/O connector panel (74-26407-01) Internal cable for physical console (17-02168-01) DEC LANcontroller 400 Installation Guide (EK-DEMNA-IN) DEC LANcontroller 400 Console User's Guide (EK-DEMNA-UG) |  |

| VAX 6000<br>capinet kit                      | CK-DEMNA-KD | Ethernet I/O connector panel (74-26407-41)<br>8-ft. internal Ethernet cable (17-01496-02)<br>Blank panel (74-26407-01)<br>Ethernet loopback connector (12-22196-02)                                                                                                                                                                 |  |

| VAX 9000<br>Model 2xx<br>cabinet kit         | CK-DEMNA-KE | Ethernet I/O connector panel (70-27894-01) 3-ft. internal Ethernet cable (17-01496-01) Ethernet loopback connector (12-22196-02)                                                                                                                                                                                                    |  |

| VAX 9000<br>Model 4xx<br>cabinet kit         | CK-DEMNA-KM | Ethernet I/O connector panel (70-27894-01)<br>8-ft. internal Ethernet cable (17-01496-02)<br>Ethernet loopback connector (12-22196-02)                                                                                                                                                                                              |  |

## 1.3.2 Status LEDs

The DEMNA module has two status-indicator lights:

- One DEMNA OK LED (yellow)—the self-test LED required by the XMI bus specification

- One External Loopback LED (green)

Immediately after power-up or reset, both status-indicator lights are off. If all the tests in the self-test pass (a. de from the LANCE external loopback test), the self-test lights the yellow DEMNA OK LED. If the LANCE external loopback test passes (indicating that the DEMNA can transmit and receive a loopback packet over the network), the self-test lights the green External Loopback LED.

# 2 Installation

This chapter explains how to install the DEMNA option into a system that has an XMI bus. The installation procedure has three major parts:

- Hardware Installation

- Verification of Hardware Installation

- Verification of DEMNA Operation in Network

It is very important to perform all parts of the installation procedure. Do not skip any part of the procedure.

The installation procedure does not describe how to install an Ethernet transceiver. For instructions on installing an Ethernet transceiver, see the installation guide for the host computer system.

#### WARNINGS

POWER OFF—Shut off system power and disconnect the system power cord before performing any procedure in this chapter.

WEAR ESD WRIST STRAP—You must wear an antistatic wrist strap that is connected to the processor cabinet whenever you work inside the cabinet.

USE CONDUCTIVE CONTAINERS—Whenever you remove a circuit board from an XMI card cage, place it in a conductive container.

## 2.1 HARDWARE INSTALLATION

When installing a DEMNA in a VAX 6000 system, use the procedure in Section 2.1.1. When installing a DEMNA in a VAX 9000 system, use the procedure in Section 2.1.2.

## 2.1.1 Hardware Installation in a VAX 6000 System

Up to three DEMNAs can be installed in an XMI card cage in a VAX 6000 system.

The following steps describe how to install the DEMNA hardware in a VAX 6000 system:

- 1 Power down the host computer system by:

- a. Turning the Power switch to the Off position

- b. Setting the system circuit breaker in the rear to Off

- 2 Open front door of the cabinet.

- Put on the ESD wrist strap that is attached to the system chassis.

This grounds you and thus prevents you from damaging the electronic components by discharging static electricity.

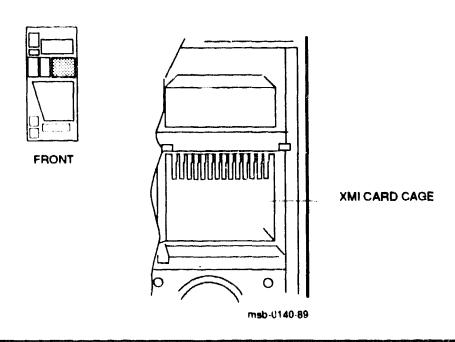

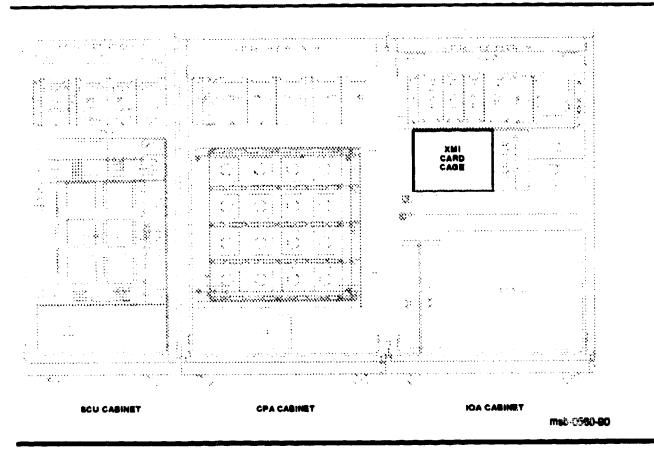

- 4 Locate the XMI card cage. Figure 2-1 shows the location of the XMI card cage in a VAX 6000 system.

- 5 Remove the door on the front of the XMI card cage.

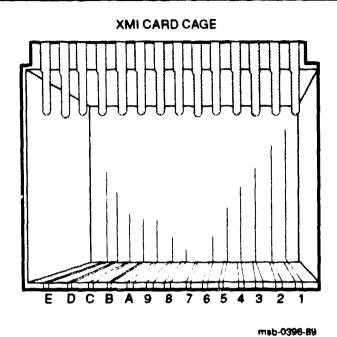

- Determine the slot into which the DEMNA should be installed. In a VAX 6000 system, the DEMNA can be put into any of the following slots: 1-4, B-E (see Figure 2-2). In general, the DEMNA should be put in the highest-numbered slot available within the ranges specified above. CPUs are usually put in lower-numbered slots.

- 7 Lift the lever to open the chosen slot.

- 8 Slide the DEMNA module into the slot until it stops: this is a zero-insertion-force card cage.

- 9 Close the locking lever.

- 10 Replace the door on the front of the card cage.

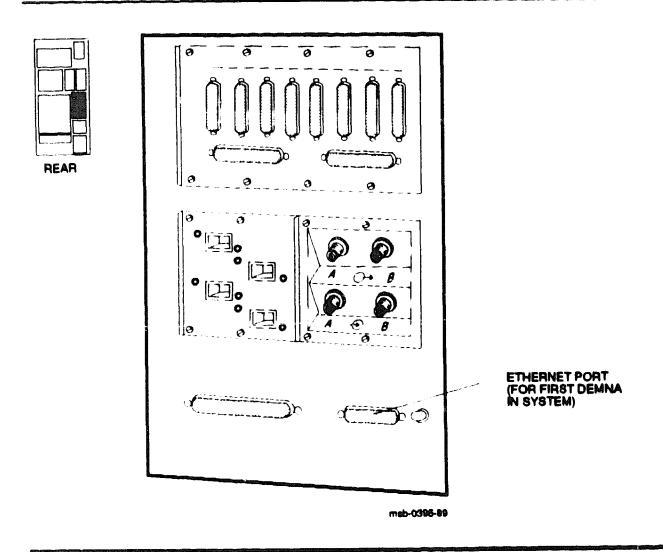

- 11 Install an I/O connector panel (74-26407-41) for an Ethernet connector over one of the bulkhead cutouts. If you are replacing the first Ethernet controller in the system, this is unnecessary.

Figure 2-1 Location of XMI Card Cage in a VAX 6000 System

## 12 Install the internal Ethernet cable as follows:

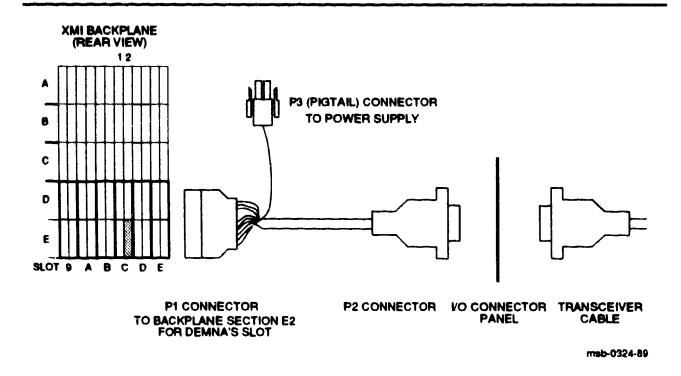

a. Connect the P1 connector of the internal Ethernet cable to backplane segment E2 for the DEMNA slot (see Figure 2-3). The connector is right-side-up when the key on the connector is on the right. The P1 connector is not uniquely keyed for backplane segment E2. It is thus possible to insert the connector into the wrong backplane segment.

## CAUTION

Do not connect the DEMNA to the network until you have verified the DEMNA installation. If the DEMNA cabling is connected to the wrong slot, an arbitrary signal may be output on the transmit line, which might bring down the entire network.

Figure 2-2 XMI Card Cage Slots

- b. Attach the P2 connector of the internal Ethernet cable to the I/O connector panel. (If you are replacing the first Ethernet controller in a VAX 6000 system, connect the P2 connector to the system interconnect panel. The P2 connector plugs into the rear of the Ethernet connector on the panel. Figure 2-4 shows the system interconnect panel for a VAX 6000 Model 400 system.)

- c. Connect the pigtail connector (P3) from the internal Ethernet cable to a +15V 2-prong connector (J2) from any of the H7214 power supplies. These power supplies are located in the rear of the cabinet.

#### NOTE

All the connectors from the power supply may already be used. In this case, the external transceiver cable must not be connected directly to an H4000 transceiver, a DESTA (a thin-wire box), or a DECOM broadband transceiver—none of which has its own power supply. The transceiver cable may, however, be connected to one of the following devices, each of which has its own

## power supply and which, in turn, may be connected to an H4000:

- A DELNI

- A DEMPR (2 thin-wire version of the DELNI)

- A DEBET (a bridge)

Figure 2-3 Internal Ethernet Cable Connections

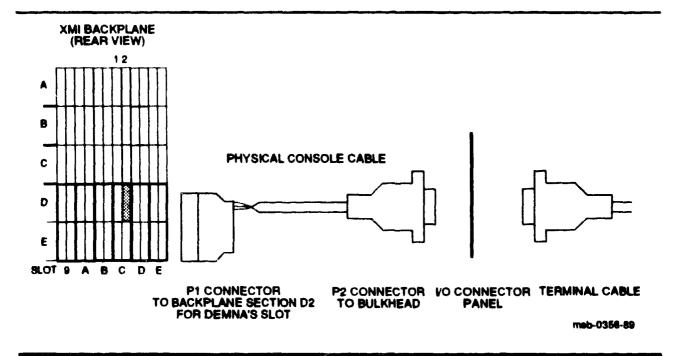

- 13 If a physical console is going to be used, install the internal cable for the physical console as follows:

- a. Install an I/O connector panel (74-26407-32) for the cable over one of the bulkhead cutouts.

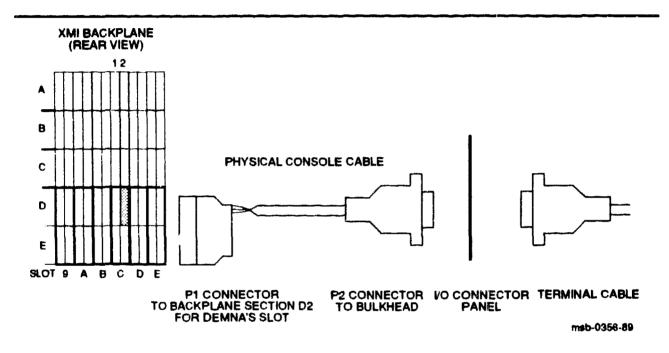

- b. Connect the P1 connector of the cable to backplane segment D2 for the DEMNA slot (see Figure 2-5). The connector is right-side-up when the key on the connector is on the right. The P1 connector is not uniquely keyed for backplane segment D2. It is thus possible to insert the connector into the wrong backplane segment.

c. Attach the P2 connector of the cable to the I/O connector panel.

Figure 2-4 System Interconnect Panel-VAX 6000 Model 400 System

Figure 2-5 Internal Cable for Physical Console

## 2.1.2 Hardware Installation in a VAX 9000 System

Up to four DEMNAs can be installed per XMI card cage in a VAX 9000 system.

The following steps describe how to install the DEMNA hardware in a VAX 9000 system:

- 1 Power down the host computer system by:

- a. Turning the Power switch to the Off position

- b. Setting the appropriate system circuit breaker(s) to Off

- 2 Open front door of the appropriate cabinet.

- 3 Put on the ESD wrist strap that is attached to the system chassis. This grounds you and thus prevents you from damaging the electronic components by discharging static electricity.

- 4 Locate the XMI card cage into which the DEMNA is to be installed. Figure 2-6 shows the location of the XMI card cage in a VAX 9000 Model 2xx. Figure 2-7 shows the location of the XMI card cage in a VAX 9000 Model 4xx.

Figure 2-6 Location of XMI Card Cage in a VAX 9000 Model 2xx System

2--6

Figure 2-7 Location of XMI Card Cages in a VAX 9000 Model 4xx System

- 5 Open the door on the front of the appropriate XMI card cage.

- Determine the slot into which the DEMNA should be installed (see Figure 2–8). In a VAX 9000 system, the DEMNA can be put into any XMI slot except slot 7 or 8.

- 7 Lift the lever to open the chosen slot.

- 8 Slide the DEMNA module into the slot until it stops: this is a zero-insertion-force card cage.

- 9 Close the locking lever.

- 10 Close the door on the front of the XMI card cage.

- 11 Install an I/O connector panel (70-27894-01) for an Ethernet connector over one of the bulkhead cutouts. (If you are installing the second DEMNA in the cabinet, this is unnecessary, since the I/O connector panel accommodates two DEMNAs.)

Figure 2-8 XMI Card Cage

msb-0396-89

## 12 Install the internal Ethernet cable as follows:

a. Connect the P1 connector of the internal Ethernet cable to backplane segment E2 for the DEMNA slot (see Figure 2-9). The connector is right-side-up when the key on the connector is on the right. The P1 connector is not uniquely keyed for backplane segment E2. It is thus possible to insert the connector into the wrong backplane segment.

#### CAUTION

Do not connect the DEMNA to the network until you have verified the DEMNA installation. If the DEMNA cabling is connected to the wrong slot, an arbitrary signal may be output on the transmit line, which might bring down the entire network.

b. If you are installing the second DEMNA in the cabinet, remove the plate over the second cutout of the I/O connector panel.

c. Attach the P2 connector of the internal Ethernet cable to the I/O connector panel.

Figure 2-9 Internal Ethernet Cable Connections

d. Connect the pigtail connector (P3) from the internal Ethernet cable to a +15V 2-prong connector on the power distribution adapter for the XMI card cage (see Figure 2-10). The J2 connector on the power distribution adapter is connected to the main power supply (H7214). The J1, J3, J5 connectors are connected to the auxiliary power supply. Table 2-1 summarizes the power connections for VAX 9000 systems.

| Table 2-1 | <b>Power Connection</b> | for Internal Ethernet | Cable—VAX 9000 Systems |

|-----------|-------------------------|-----------------------|------------------------|

|-----------|-------------------------|-----------------------|------------------------|

| System                | Maximum Number of<br>DEMNAs Per Card Cage | Power Connection                                                                                                                 |

|-----------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| VAX 9000<br>Model 2xx | 4                                         | Any connector on the power distribution adapter (part no. 54-19045-01) located in the rear of the cabinet on the left-hand rails |

| VAX 9000<br>Model 4xx | 4                                         | Any connector on the power distribution adapter (part no. 54-19045-01) located in the rear of the cabinet on the right-hand rail |

Figure 2-10 Power Distribution Adapter—VAX 9000 Systems

- 13 If a physical console is going to be used, install the internal cable for the physical console as follows:

- a. Install an I/O connector panel (70-28010-01) for the cable over one of the bulkhead cutouts.

- b. Connect the P1 connector of the cable to backplane segment D2 for the DEMNA slot (see Figure 2-11). The connector is right-side-up when the key on the connector is on the right. The P1 connector is not uniquely keyed for backplane segment D2. It is thus possible to insert the connector into the wrong backplane segment.

c. Attach the P2 connector of the cable to the I/O connector panel.

Figure 2-11 Internal Cable for Physical Console

## 2.2 VERIFICATION OF HARDWARE INSTALLATION

## **CAUTION**

It is very important that you verify that the DEMNA in properly installed. If the DEMNA is improperly installed, you may bring down the entire ne work when you connect the DEMNA to the network.

Follow these steps to verify that the DEMNA is properly installed

- 1 Connect the loopback connector (part number 12-22196-02) to the Ethernet connector (P2 connector) of the internal Ethernet cable

- 2 Set the appropriate system circuit breaker(s) to On.

- 3 Turn on the system power This causes each module in the system to execute its self-test.

- Verify that the green LED on the loopback connector is lit, indicating that the pigtail (P3) connector of the internal Ethernet cable is properly connected and is supplying +12V for the transceiver. If the LED is not lit, power down the system, make sure that the pigtail connector is connected to the right power connection, and reseat the pigtail connector. Continue with step 2.

- Verify that the DEMNA passes both self-test (the yellow DEMNA OK LED lights) and the LANCE external loopback test (the green External Loopback LED lights). (See Section 3.2.1 for further information on the DEMNA LEDs.)

- If the self-test and/or external loopback test fails, check to see that the DEMNA module is properly seated in the card cage and that all three connectors of the internal Ethernet cable are properly installed.

- 7 If the module continues to fail self-test, swap in a different DEMNA module if one is available. You can also try installing the module in a different slot.

- If the module still fails self-test, run the DEMNA ROM-based diagnostics (RBDs), which are described in the DEC LANcontroller 400 Technical Manual.

#### 2.3 VERIFICATION OF DEMNA OPERATION IN NETWORK

Proper operation of the DEMNA was verified up to the system bulkhead (Ethernet connector) in Section 2.2. Now, follow these steps to verify that the DEMNA can communicate with other network nodes:

- 1 Connect the external transceiver cable to the P2 (Ethernet) connector of the internal Ethernet cable (available at the system bulkhead) or, for the first Ethernet controller in a VAX 6000 system, to the Ethernet connector on the system interconnect panel.

- 2 Boot the operating system.

- 3 Configure the network database and start the network software.

- 4 If the system is unable to communicate over the network, verify that the network software is installed and configured properly.

- If the network software is properly installed and configured and the system is still unable to communicate over the network, shut down

the system and check the transceiver and the transceiver cable as follows:

- a. Disconnect the external Ethernet transceiver cable (BNE3) at the transceiver end.

- b. Install the loopback connector (12-22196-02) on the cable.

- c. Run the DEMNA self-test and observe one of the following:

- If the External Loopback LED on the DEMNA module lights, the transceiver is bad. Replace the transceiver, reconnect the cable to the new transceiver, and rerun the self-test to verify proper operation. No further action is required.

- If the External Loopback LED on the DEMNA module does not light, the transceiver cable is bad and/or the P3 power connection for the internal Ethernet cable is not good. First, check the LED on the loopback connector. If the LED did not light, reseat the P3 connector and rerun the self-test. If the LED on the loopback connector is lit, replace the transceiver cable.

#### 2.4 INTERNAL ETHERNET CABLE

The internal Ethernet cable connects to the XMI backplane at the DEMNA slot and provides Ethernet signals and power (if required) to an H4000 transceiver or other network interface device. See Table 1-2 for part numbers.

The cable has three connectors (Figure 2-3): P1, P2, and P3. The P1 connector connects to segment E2 on the XMI backplane opposite the DEMNA slot. The P2 connector is an industry-standard Ethernet connector that connects to an I/O connector panel on the bulkhead or to the rear of the Ethernet connector on the system interconnect panel in a VAX 6000 system. The P3 (pigtail) connector is a +15V direct-current power connection that supplies power to a device (such as an H4000 transceiver, a DESTA thin-wired box, or a DECOM broadband transceiver) that does not have its own power supply. The pigtail connector should be plugged in regardless of the type of transceiver.

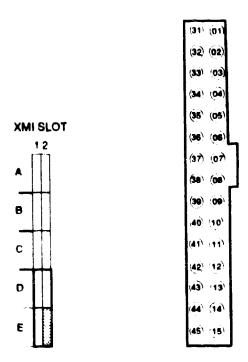

Figure 2-12 shows the P1 connector pinouts of the internal Ethernet cable. Table 2-2 describes these pinouts. Figure 2-13 shows the pinouts for the P2 connector of the internal Ethernet cable, and Table 2-3 describes these pinouts.

Figure 2-12 P1 Connector Pinouts of Internal Ethernet Cable

LOOKING AT BACKPLANE

msb-0325-89

Table 2-2 P1 Connector Pinouts of Internal Ethernet Cable

| Pin        | Signal                                    | Description                                                  |

|------------|-------------------------------------------|--------------------------------------------------------------|

| E01-E04    | Unconnected                               |                                                              |

| E05-E09    | Logic Ground                              |                                                              |

| E10<br>E11 | Ethernet Collision L Ethernet Collision H | Differential collision detect signals from the Ethernet bus. |

| E12<br>E13 | Ethernet Receive L<br>Ethernet Receive H  | Differential receive signals from the Ethernet bus.          |

| E14<br>E15 | Ethernet Transmit L Ethernet Transmit H   | Differential transmit signals to the Ethernet bus.           |

Figure 2-13 P2 Connector Pinouts of Internal Ethernet Cable

msb-0326-89

Table 2-3 P2 Connector Pinouts of Internal Ethernet Cable

| Pin           | Signal                                    | Description                                                                   |

|---------------|-------------------------------------------|-------------------------------------------------------------------------------|

| 1             | Shield                                    |                                                                               |

| <b>8</b><br>5 | Collision Presence H Collision Presence L | Differential signals that indicate a failure of the collision detection logic |

| 3<br>10       | Transmit H<br>Transmit L                  | Differential transmit signals to the Ethernet bus                             |

| 4             | Reserved                                  |                                                                               |

| 5<br>12       | Receive H<br>Receive L                    | Differential receive signals from the<br>Ethernet bus                         |

| 6             | Power Return                              | Power return line                                                             |

| 7             | Reserved                                  |                                                                               |

| 8             | Reserved                                  |                                                                               |

| 11            | Reserved                                  |                                                                               |

| 13            | Power                                     |                                                                               |

| 14            | Reserved                                  |                                                                               |

| 15            | Reserved                                  |                                                                               |

#### 2.5 EXTERNAL TRANSCEIVER CABLE

The external transceiver cable runs from the Ethernet connection provided at the bulkhead or system interconnect panel to an Ethernet transceiver, such as an H4000 baseband transceiver, DECOM broadband transceiver, or DELNI local network interconnect. The cable is ordered as a separate item.

#### 2.6 INTERNAL CABLE FOR PHYSICAL CONSOLE

The internal cable for the physical console connects the XMI backplane at the DEMNA slot to the system bulkhead and provides a connector for a terminal cable. The cable is ordered as a separate item.

The cable has two connectors: P1 and P2 (see Figure 2-5). The P1 connector connects to segment D2 on the XMI backplane opposite the DEMNA slot. The P2 connector is a standard 25-pin Sub-D connector that connects to the bulkhead and is used as a connector for a terminal cable.

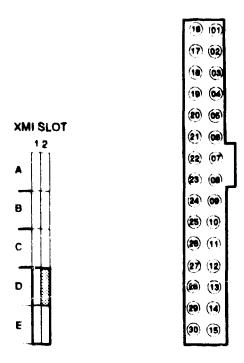

Figure 2-14 shows the P1 connector pinouts for the internal cable for the physical console. Table 2-4 describes these pinouts. Figure 2-15 shows the P2 connector pinouts for the internal cable for the physical console. Table 2-5 describes these pinouts.

Figure 2-14 P1 Connector Pinouts of Internal Cable for Physical Console

LOOKING AT BACKPLANE

msb-0327-89

Table 2-4 P1 Connector Pinouts of Internal Cable for Physical Console

| Pin    | Signal       |  |

|--------|--------------|--|

| D01    | Transmit     |  |

| D02    | Receive      |  |

| D03    | Logic Ground |  |

| D04D30 | Unconnected  |  |

Figure 2-15 P2 Connector Pinouts of Internal Cable for Physical Console

msb-0348-89

Table 2-5 P2 Connector Pinouts of Internal Cable for Physical Console

| Pin  | Signal       |

|------|--------------|

| 1    | Unconnected  |

| 2    | Transmit     |

| 3    | Receive      |

| 4-6  | Unconnected  |

| 7    | Logic Ground |

| 8-25 | Unconnected  |

#### 2.7 REMOVAL

To remove a DEMNA module, follow these steps:

- 1 Power down the host computer system by:

- a. Turning the Power switch to the Off position

- b. Setting the appropriate system circuit breaker(s) to Off

- 2 Open the appropriate cabinet.

- 3 Make sure you are wearing an ESD wrist strap that is attached to the system chassis.

- Open or remove the door on the front (module-insertion side) of the XMI card cage that contains the DEMNA to be removed.

- 5 Locate the desired card cage slot.

- 6 Lift the lever to open the slot.

- 7 Slide the module out of the card cage slot.

- 8 Put the module into a conductive container.

- 9 Close the locking lever.

- 10 If another DEMNA will not be installed:

- a. Close or replace the door on the front of the KMI card cage from which the DEMNA was removed.

- b. Remove the cables from the slot that contained the DEMNA.

- c. Close the cabinet.

<pre

### Power-Up Self-Test

The DEMNA power-up self-test consists of ROM-resident diagnostic routines that run automatically on power-up or reset. The power-up self-test verifies that the hardware at the node is operational and that the DEMNA can transmit and receive a loopback packet over the network.

Since the routines are contained in ROM, their execution requires no operating system. The self-test routines are thus stand-alone programs independent of any software environment.

#### 3.1 HOW TO RUN SELF-TEST

There are several ways of running self-test for the DEMNA:

- On system power-up—When the user powers up the host system, the DEMNA automatically runs power-up self-test. Front panel controls vary among host systems; see the system Owner's Manual for the specific system.

- On XMI system reset—For VAX 6000 systems: When the user presses the reset or restart button on the host system's front panel, the system goes through its reset sequence, which causes each XMI node to run its own self-test. For VAX 9000 systems: The user can issue the following console command to reset a particular XMI card cage:

>>>UNJAM /XJA=n

where n is the unit number of the XJA adapter for the XMI card cage. If the XJA unit number is not supplied, the command resets all XMI card cages in the system.

Running self-test as a ROM-based diagnostic (RBD)—A Digital customer service engineer can invoke the self-test as an RBD from the system console of a VAX 6000 or VAX 9000 system or from the DEMNA physical console (a terminal attached directly to the DEMNA). This is the same diagnostic that runs during power-up or reset self-test.

Example 3-1 shows how to use VAX console commands on a VAX 6000 system to run the self-test on a DEMNA located at XMI node 3. For a description of the Z command used in this example, see the system Owner's Manual.

#### Example 3-1 Running Self-Test on a VAX 6000 System

Example 3-2 shows how to use VAX console commands on a VAX 9000 system to run the self-test on a DEMNA at node E through XJA number 2. For a description of the Z command used in this example, see the system Owner's Manual.

### Example 3-2 Running Self-Test on a VAX 9000 System

If you do not know which XMI node the DEMNA is at, use the SHOW CONFIGURATION command at the system console prompt to locate the DEMNA.

Another way of locating the DEMNA node is to use the EXAMINE command to read the Device (XDEV) Register at each node until you find the DEMNA, which has a device type of 0C03 (hex). A module's XDEV Register is always at the module's base address.

#### 3.2 REPORTING SELF-TEST RESULTS

Test results (pass or fail) are indicated by LEDs on the module and by the DEMNA Power-Up Diagnostic (XPUD) Register.

#### 3.2.1 Self-Test Results in LEDs

There are two status-indicator lights on the module:

- 1 yellow DEMNA OK LED

- 1 green External Loopback LED

The location of the LEDs is shown in Figure 3-1.

The yellow DEMNA OK LED shows the status of the module after the node self-test. The green External Loopback LED indicates whether the DEMNA passed the LANCE external loopback test, which tests the DEMNA's ability to transmit and receive a loopback packet over the network.

At power-up or reset, both LEDs are off. If the DEMNA passes all the executed tests (excluding the LANCE external loopback test), the self-test lights the yellow DEMNA OK LED; otherwise, this LED remains off. If the LANCE external loopback self-test passes, the self-test lights the green External Loopback LED; otherwise this LED remains off.

### 3.2.2 Self-Test Results in the Power-Up Diagnostic Register

The Power-Up Diagnostic (XPUD) Register indicates which tests in the self-test diagnostic passed. In addition, the Self-Test Complete (STC) bit indicates whether the self-test has completed execution. See Appendix B for a detailed description of the XPUD Register.

| DEMNA OK LED (YELLOW) EXTERNAL LOOPBACK LED (GREEN) | CONNECTOR EDGE |

|-----------------------------------------------------|----------------|

#### 3.3 INTERPRETING TEST RESULTS

If the External Loopback LED fails to light, indicating that the LANCE external loopback self-test failed, this does not necessarily indicate that a DEMNA component failed self-test. The problem could be a bad cable, bad Ethernet transceiver connector, improper seating of the transceiver cable, or simply that the DEMNA is disconnected from the transceiver. In any case, such an error condition prevents the DEMNA from transmitting or receiving Ethernet packets.

If the XPUD Register indicates that all of the self-test routines failed, the problem is probably the CVAX, ROM, or bus transceivers.

Self-test could also fail because of a systemwide fault. For example, a faulty power supply or missing XMI bus terminators could be the problem. Make sure that system power is OK and check for other possible systemwide faults.

Note also that the External Loopback LED does not light if another test in the self-test diagnostic fails. When another self-test fails, the external loopback test is not executed.

After a problem discovered by the self-test has been corrected, the DEMNA LED(s) will light only if the self-test is rerun. However, if the self-test is not rerun, the DEMNA will still function properly even though the LED(s) don't light.

#### 3.4 TESTED COMPONENTS

The self-test tests the following components and functions on the DEMNA module:

- CVAX

- EPROM

- EEPROM

- CVAX ROM

- All RAM

- System Support Chip (SSC)

- CVAX Interrupt Request (IRQ) lines

- Gate Array

- LANCE chip

#### 3.5 UNTESTED COMPONENTS AND FUNCTIONS

The following components and functions are not tested:

- A complete CVAX instruction set

- Ethernet interface logic functions:

- More (multiple retries of packet transmission)

- One (one retry of a packet transmission)

- Babble error

- Time domain reflectometry

- Late collision

- Loss of carrier

The datamove logic, which is implemented in the gate array, is tested in loopback mode only.

### **Environmental Requirements**

| Operating<br>Environment |                                                                                                     |

|--------------------------|-----------------------------------------------------------------------------------------------------|

| Temperature              | 5°C to 50°C (41°F to 122°F)                                                                         |

| Humidity                 | 10% to 95% with maximum wet bulb of 32°C (89.6°F) and minimum dew point of 2°C (36°F) noncondensing |

| Altitude                 | To 2.4 km (8,000 ft)                                                                                |

| Storage Environm         | ent                                                                                                 |

| Temperature              | -40°C to 66°C (-40°F to 151°F)                                                                      |

| Humidity                 | To 95% nencondensing                                                                                |

| Altitude                 | To 9.1 km (30,000 ft)                                                                               |

### B

### Registers

This appendix describes the DEMNA registers that are useful for troubleshooting problems that may occur during installation. Table B-1 summarizes these registers. Table B-2 explains the access types for these registers, as well as the bit types for the registers. Each register is then described in detail.

Table B-1 Registers Useful During Installation—Summary

| Name                                      | Mnemonic       | XMI<br>Address    | Type <sup>1</sup> | Description                                                                                                                                                                    |

|-------------------------------------------|----------------|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                                    | XDEV           | bb + 0            | RO                | Indicates the XMI node's device type and device firmware revision level.                                                                                                       |

| Bus Error                                 | XBER           | bb + 4            | R/W               | Records XMI bus errors and loopback errors.                                                                                                                                    |

| Power-Up Diagnostic                       | XPUD           | bb + 10C          | RO                | Indicates whether self-test has completed and which tests in the self-test passed.                                                                                             |

| Failing Address Failing Address Extension | XFADR<br>XFAER | bb + 8<br>bb + 2C | RO<br>RO          | Provide information on failing XMI transactions initiated by the DEMNA.                                                                                                        |

| Gate Array CSR                            | GACSR          | None              |                   | Provides status on the gate array. This register is part of the fatal error block and nonfatal error block, which are described in the DEC LANcontroller 400 Technical Manual. |

<sup>&</sup>lt;sup>1</sup>With respect to the port driver

### Registers

| Table B-2 | Abbreviations for Bit Types |                                   |  |  |

|-----------|-----------------------------|-----------------------------------|--|--|

|           | Abbreviation                | Definition                        |  |  |

|           | 0                           | Initialized to logic level zero   |  |  |

|           | 1                           | Initialized to logic level one    |  |  |

|           | X                           | Initialized to either logic state |  |  |

|           | RO                          | Read only                         |  |  |

|           | R/W                         | Read/write                        |  |  |

|           | R/W1C                       | Read/cleared by writing a 1       |  |  |

### Device Register (XDEV)

The Device Register identifies the DEMNA device type, hardware revision, and EEPROM firmware revision. The device type for the DEMNA is 0C03 (hexadecimal).

The port loads the Device Register on power-up or reset. The port driver reads the Device Register to determine the module device type before attempting to initialize the port.

#### **ADDRESS**

Nodespace base address + 0

| 31     | 16         | 15 0        |

|--------|------------|-------------|

| Device | e Revision | Device Type |

msb-0343-89

#### BITS<31:16>

Name:

**Device Revision**

Mnemonic:

DREV

Type:

RO. 0

Indicates the device revision of the DEMNA. The high-order byte of the field is the hardware revision number, which indicates the functional revision of the hardware. This is identical to the hardware functional revision indicated on the module label. The low-order byte of the field is the revision number of the loaded firmware. If the EEPROM firmware is loaded (which is normally the case), the firmware revision field indicates the EEPROM firmware revision. However, if the EPROM firmware is loaded (which occurs if the EEPROM fails selftest), the firmware revision field indicates the EPROM firmware revision.

The hardware revision field is decoded as follows for the first 10 hardware revisions of the DEMNA. Note that letters G and I, as well as their corresponding codes, are skipped.

| Code (hex) | Hardware Revision Level |  |

|------------|-------------------------|--|

| 01         | A                       |  |

| 02         | В                       |  |

| 03         | С                       |  |

| 04         | D                       |  |

| 05         | E                       |  |

| 06         | F                       |  |

| 08         | н                       |  |

| 0 <b>A</b> | J                       |  |

| ов         | K                       |  |

| OC         | L                       |  |

The firmware revision field is decoded as follows for the first 10 EEPROM firmware revisions for a given hardware revision level.

| Code (hex) | EEPROM Firmware Revision Level |  |

|------------|--------------------------------|--|

| 01         | 01                             |  |

| 02         | 02                             |  |

| 03         | 03                             |  |

| 04         | 04                             |  |

| 05         | 05                             |  |

| 06         | 06                             |  |

| 07         | 07                             |  |

| 08         | 08                             |  |

| 09         | 09                             |  |

| 0 <b>A</b> | 10                             |  |

Note that the firmware revision levels of both the EEPROM and the EPROM are zeroed when the hardware revision level changes.

# Registers Device Register (XDEV)

Table B-3 shows how the Device Revisions field is encoded for the first three firmware revisions of hardware revision F and for the first firmware revision of hardware revision H.

Table B-3 Example of Device Revision Field

| Hex Value | Hardware Revision | Firmware Revision |  |

|-----------|-------------------|-------------------|--|

| 0600      | F                 | 0                 |  |

| 0601      | F                 | 1                 |  |

| 0602      | F                 | 2                 |  |

| 0603      | F                 | 3                 |  |

| 0800      | Н                 | 0                 |  |

#### BITS<15:0>

Name: Device Type

Mnemonic: XDEV

Type: RO, 0

A value of 0C03 (hex) indicates that the adapter is a DEMNA module.

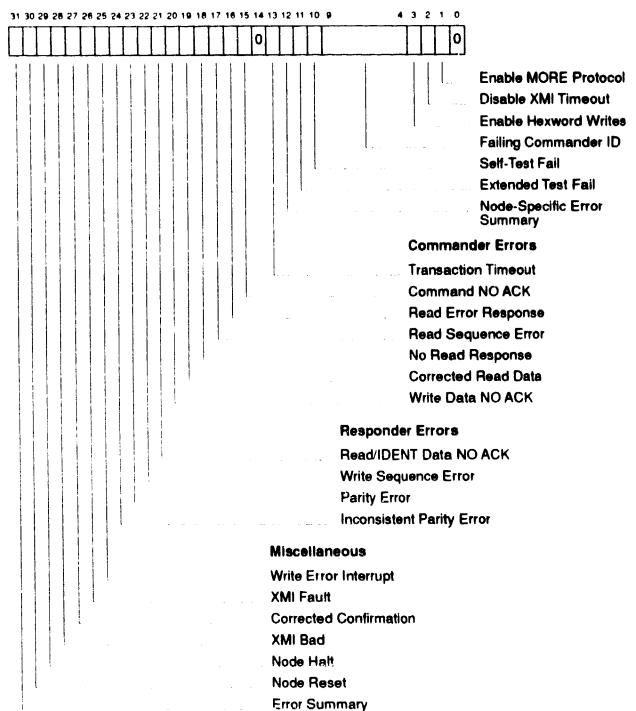

### **Bus Error Register (XBER)**

The Bus Error Register contains error status on a failed XMI transaction. This status includes the failed command, commander ID, and an error bit that indicates the type of error that occurred. This status remains locked until software resets the error bit(s).

#### **ADDRESS**

Nodespace base address + 0000 0004

msb-0344-89

#### BIT<31>

Name:

**Error Summary**

Mnemonic:

ES

Type:

RO, 0

ES represents the logical OR of the command error bits and the Self-Test Fail bit in this register. Therefore, ES asserts when any error bit asserts.

#### BIT<30>

Name:

**Node Reset**

Mnemonic:

**NRST**

Type:

**R/W**, 0

The host writes a one to NRST to cause the DEMNA to execute a complete power-up reset. This sequence is similar to the response caused by a real power-up sequence, which is triggered by the assertion and deassertion of XMI DC LO L. The DEMNA asserts XMI BAD L until the self-test completes successfully. Nodes should not access the DEMNA from the time it is reset until it completes self-test (or the maximum self-test time is exceeded).

While the DEMNA is responding to node reset, it does not access other nodes on the XMI bus. In response to a real power-up sequence (caused by XMI DC LO L), the NRST bit will be cleared. However, when set by the host to cause a node reset, the bit remains set, thus indicating to the DEMNA CVAX that the host issued a node reset. The DEMNA self-test clears this bit once the node reset has completed.

#### EIT<29>

Name:

Node Halt

Mnemonic:

**NHALT**

Type:

R/W, 0

The host sets NHALT to force the DEMNA to execute its halt sequence. The halt causes the DEMNA to go into a quiet state and retain as much state information as possible. Firmware execution jumps to the initialization code in EPROM (Boot ROM), shuts down the port, and loops on the NHALT bit. When the host clears NHALT, the DEMNA executes its restart sequence, which is identical to the power-up/reset sequence, except that the DEMNA does not execute its self-test, clear its internal data link or error counters, or clear its fatal and nonfatal error blocks.

#### BIT<28>

Name:

XMI BAD

Mnemor.

**XBAD**

T-/pe:

R0. 1

The DEMNA does not use this bit.

#### BIT<27>

Name:

**Corrected Confirmation**

Mnemonic:

CC

Type:

R/W1C. 0

This bit sets when the DEMNA detects a single-bit CNF error. Single-bit CNF errors are automatically corrected by the XCLOCK chip in the XMI Corner.

BIT<26>

Name:

**XMI FAULT**

Mnemonic:

**XFAULT**

Type:

RO, 0

The DEMNA does not use this bit.

BIT<25>

Name:

Write Error Interrupt

Mnemonic:

WEI

Type:

RO, 0

The DEMNA does not use this bit.

BIT<24>

Name:

Inconsistent Parity Error

Mnemonic:

**IPE**

Type:

RO. 0

The DEMNA does not use this bit.

BIT<23>

Name:

Parity Error

Mnemonic:

PE

Type:

R/W1C, 0

When set, indicates that the DEMNA has detected a parity error on an XMI cycle.

#### BIT<22>

Name:

Write Sequence Error

Mnemonic:

WSE

Type:

R/W1C, 0

When set, indicates that an XMI node attempting a write to the DEMNA aborted the write transaction due to missing data cycles. Only XMI responder nodes are required to implement this bi\* If not implemented, nodes return zero.

#### BIT<21>

Name:

Read/IDENT Data NO ACK

Mnemonic:

**RIDNAK**

Type:

R/W1C, 0

When set, indicates that a Read or IDENT data cycle (GRDn) transmitted by the DEMNA has received a NO ACK confirmation.

#### BIT<20>

Name:

Write Data NO ACK

Mnemonic:

**WDNAK**

Type:

R/W1C, 0

When set, indicates that a Write data cycle (WDAT) transmitted by the DEMNA has received a NO ACK confirmation.

#### BIT<19>

Name:

**Corrected Read Data**

Mnemonic:

CRD

Type:

R/W1C, 0

When set, indicates that the node has received a CRDn read response.

#### BIT<18>

Name:

No Read Response

Mnemonic:

NRR

Type:

R/W1C, 0

When set, indicates that a transaction initiated by the DEMNA failed due to a read response timeout.

#### BIT<17>

Name:

Read Sequence Error

Mnemonic:

RSE

Туре:

F/W1C, 0

When set, indicates that a transaction initiated by the DEMNA failed due to a read sequence error.

#### BIT<16>

Name:

Read Error Response

Mnemonic:

RER

Type:

R/W1C. 0

When set, RER indicates that a node has received a Read Error

Response.

#### BIT<15>

Name:

Command NO ACK

Mnemonic:

**CNAK**

Type:

R/W1C. 0

When set, indicates that a command cycle transmitted by the DEMNA has received a NO ACK confirmation caused either by a reference to a nonexistent memory location or by a command cycle parity error.

#### BIT<14>

Name:

Reserved

Mnemonic:

None

Type:

**RO, 0**

Reserved; must be zero.

#### BIT<13>

Name:

Transaction Timeout

Mnemonic:

TTO

Type:

R/W1C, 0

When set, indicates that a transaction initiated by the DEMNA failed due to a transaction timeout.

#### BIT<12>

Name:

**Node-Specific Error Summary**

Mnemonic:

**NSES**

Type:

RO. 0

When set, NSES indicates that a node-specific error condition has been detected. The DEMNA does not use this bit.

#### BIT<11>

Name:

Extended Test Fail

Mnemonic:

ETF

Type:

**RO**, 0

This bit is not used by the DEMNA.

#### BIT<10>

Name:

Self-Test Fail

Mnemonic:

STF

Type:

R/W1C, 1

When the STF bit is set, indicating that the DEMNA has not passed self-test, the DEMNA hardware asserts XMI BAD L on the XMI bus. When the STF bit is cleared, indicating that the DEMNA has passed self-test, the hardware clears the STF bit, thus causing the DEMNA to deassert XMI BAD L.

#### BITS<9:4>

Name:

Failing Commander ID

Mnemonic:

**FCID**

Type:

RO

Bits <9:6> log the commander ID of a failing transaction during a command cycle. The failing commander ID is recorded for command errors detected by XBER bits <20> and <18:13>. Bits <5:4> indicate the type of operation that failed: 00 = a failed peek or interrupt operation; 01 = a failed datamove operation.

#### BIT<3>

Name:

**Enable Hexword Write**

Mnemonic:

**EHWW**

Type:

RO. 0

The DEMNA does not use this bit.

#### BIT<2>

Name:

Disable XMI Timeout

Mnemonic:

**DXT0**

Type:

**RW**, 0

This bit enables or disables the reporting of all XMI timeouts by a commander. When this bit is set, the node will never encounter a No Read Response (NRR) error or a transaction timeout (TTO) if retries are disabled.

#### BIT<1>

Name:

**Enable MORE Protocol**

Mnemonic:

**EMP**

Type:

**RW**, 0

When cleared, prevents the gate array from asserting the More signal on the XMI bus. When set, enables the DEMNA gate array to assert the More signal.

#### BITS<C>

Name:

Reserved

Mnemonic:

None

Type:

RO. 0

Reserved; must be zero.

### Power-Up Diagnostic Register (XPUD)

The XPUD Register displays the results of the DEMNA self-test, which runs automatically on power-up or reset. After the self-test finishes, the port driver can read the register and pass the register contents to higher-level software that can determine which DEMNA components passed self-test.

The XPUD Register is treated as follows:

- The DEMNA initializes the XPUD Register to all zeros on power-up or reset.

- When a piece of DEMNA logic passes self-test, its corresponding bit in the XPUD Register sets.

- If a piece of logic fails self-test, the corresponding bit remains cleared.

The XPUD Register of a DEMNA that passes self-test has a value of FFFFC0007 (if there are no error history entries) or FFFFC027 (if there are error history entries).

## Registers Power-Up Diagnostic Register (XPUD)

### **ADDRESS** Nodespace base address + 10C 6 5 4 3 2 1 0 г0 Firmware Initialized **External Loopback EEPROM Loaded** EPROM Loaded **Bad Diagnostic Patch** Table **EEPROM Error History Exists XNAGA** Ethernet Subsystem Parity LANCE Shared Parity RAM Shared RAM **XNADAL Timeout Logic** XNADAL Readback **EEPROM ENET PROM CVAX CVAX Parity RAM CVAX RAM** Console UART Drivers SSC Diagnostic Register **CVAX Interrupt Lines Boot ROM** Self-Test Complete

msb-0345-89

#### Registers

### Power-Up Diagnostic Register (XPUD)

#### BIT<31>

Name:

Self-Test Complete

Mnemonic:

STC

Type:

RO to port driver, 0

When set, indicates that the DEMNA self-test has completed and that the contents of the XPUD Register are valid. The register contents are invalid when the bit is cleared.

#### BIT<30>

Name:

**Boot ROM**

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that the contents of the Boot ROM (also called the EPROM) are valid.

#### BIT<29>

Name:

**CVAX Interrupt Lines**

Mnemonic:

None

Type:

F'O to port driver, 0

When set, indicates that the CVAX interrupt lines are not stuck (always asserted) or being driven by onboard logic.

#### BIT<28>

Name:

Diagnostic Register

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that all bits in the Diagnostic Register powered-up to the correct state and can be read and written.

## Registers Power-Up Diagnostic Register (XPUD)

BIT<27>

Name:

SSC

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that the SSC chip can perform all its functions.

BIT<26>

Name:

Console UART Drivers

Mnemonic:

None

Type:

RO to port driver. 0

When set, indicates that the console UART drivers are functioning

correctly.

BIT<25>

Name:

**CVAX RAM**

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that the CVAX RAM is functioning correctly (that

is, passed the CVAX RAM march test).

BIT<24>

Name:

**CVAX Parity RAM**

Mnemonic:

None

Type:

RO to port driver. 0

When set, indicates that the CVAX parity RAM is functioning

correctly.

### Power-Up Diagnostic Register (XPUD)

#### BIT<23>

Name:

**CVAX**

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that the CVAX chip is functioning correctly.

#### BIT<22>

Name:

**ENET PROM**

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that the contents of the ENET PROM are valid.

#### BIT<21>

Name:

**EEPROM**

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that the contents of the EEPROM are valid.

#### BIT<20>

Name:

XNADAL Readback

Mnemonic:

None

Type:

RO to port driver, 0

When set, indicates that the address latches and bus transceivers for the gate array/DEMNA memory bus interface are functioning correctly.

## Power-Up Diagnostic Register (XPUD)